- 您現在的位置:買賣IC網 > PDF目錄373996 > ADM1232 (Analog Devices, Inc.) Microprocessor Supervisory Circuit PDF資料下載

參數資料

| 型號: | ADM1232 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Microprocessor Supervisory Circuit |

| 中文描述: | 微處理器監控電路 |

| 文件頁數: | 2/6頁 |

| 文件大小: | 122K |

| 代理商: | ADM1232 |

–2–

REV. B

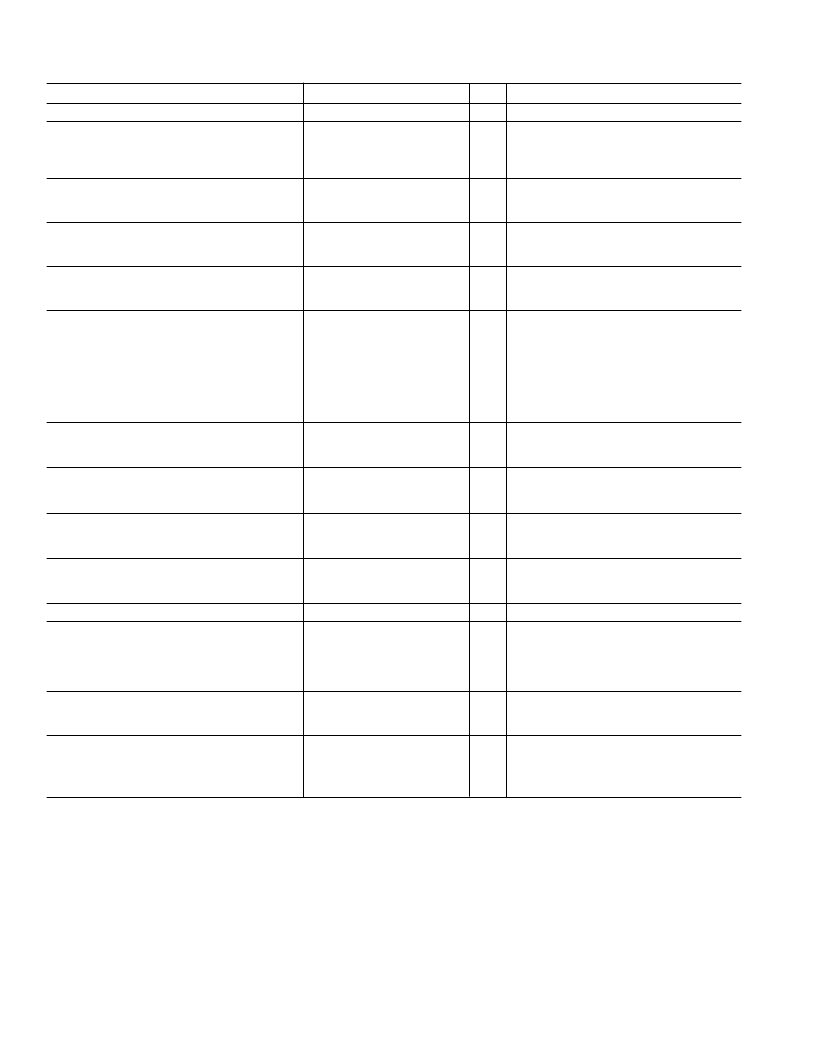

ADM1232–SPECIFICATIONS

(V

CC

= Full Operating Range, T

A

= T

MN

to T

MAX

unless otherwse noted)

P

arameter

Min

T yp

Max

Units

°

C

T est Conditions/Comments

T EMPERAT URE

POWER SUPPLY

Voltage

Current

–40

+85

T

A

= T

MIN

to T

MAX

4.5

5.0

20

200

5.5

50

500

V

μ

A

μ

A

V

IL

, V

IH

= CMOS Levels

V

IL

, V

IH

= T T L Levels

STROBE

AND

PB RESET

INPUT S

Input High Level

Input Low Level

INPUT LEAK AGE CURRENT

(

STROBE

, T OLERANCE)

T D

OUT PUT CURRENT

RESET

RESET

, RESET

OUT PUT VOLT AGE

RESET

/RESET

2.0

–0.3

V

CC

+ 0.3

+0.8

V

V

–1.0

+1.0

μ

A

μ

A

1.6

8

–8

10

–12

mA

mA

When V

CC

Is at 4.5 V–5.5 V

When V

CC

Is at 4.5 V–5.5 V

V

CC

– 0.5 V

CC

– 0.1

V

While sourcing less than 500

μ

A, RESET remains

within 0.5 V of V

on power-down until V

CC

drops below 2.0 V. While sinking less than

500

μ

A,

RESET

remains within 0.5 V of GND

on power-down until V

CC

drops below 2.0 V.

RESET

/RESET High Level

RESET

/RESET Low Level

1 V OPERAT ION

RESET Output Voltage

RESET

Output Voltage

0.4

V

V

2.4

V

CC

– 0.1

0.1

V

V

While Sourcing Less than 50

μ

A

While Sinking Less than 50

μ

A

V

CC

T RIP POINT

5%

10%

4.5

4.25

4.62

4.37

4.74

4.49

V

V

T OLERANCE = GND

T OLERANCE = V

CC

CAPACIT ANCE

Input (

STROBE

, T OLERANCE)

Output (RESET ,

RESET

)

5

7

pF

pF

T

A

= +25

°

C

T

A

= +25

°

C

PB RESET

T ime

Delay

RESET ACT IVE T IME

STROBE

Pulse Width

T imeout Period

20

1

250

ms

ms

ms

PB RESET

Must Be Held Low for a Minimum

of 20 ms to Guarantee a Reset

4

610

20

1000

70

62.5

250

500

ns

ms

ms

ms

150

600

1200

250

1000

2000

T D = 0 V

T D = Floating

T D = V

CC

V

CC

Fall T ime

Rise T ime

10

0

μ

S

μ

S

Guaranteed by Design

Guaranteed by Design

V

CC

FAIL DET ECT T O RESET OUT PUT DELAY

RESET AND

RESET

Are Logically Correct

50

μ

s

After V

Falls Below the Set T olerance Voltage

(Figure 5)

After V

CC

Rises Above the Set T olerance Voltage

250

610

1000

ms

Specifications subject to change without notice.

相關PDF資料 |

PDF描述 |

|---|---|

| ADM1232AN | Microprocessor Supervisory Circuit |

| ADM1232ARM | Microprocessor Supervisory Circuit |

| ADM1232ARN | Microprocessor Supervisory Circuit |

| ADM1232ARW | Microprocessor Supervisory Circuit |

| ADM1232AAN | Microprocessor Supervisory Circuit |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADM1232_08 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Microprocessor Supervisory Circuit |

| ADM1232A | 制造商:AD 制造商全稱:Analog Devices 功能描述:Microprocessor Supervisory Circuit |

| ADM1232AAN | 制造商:AD 制造商全稱:Analog Devices 功能描述:Microprocessor Supervisory Circuit |

| ADM1232AARM | 制造商:AD 制造商全稱:Analog Devices 功能描述:Microprocessor Supervisory Circuit |

| ADM1232AARN | 制造商:AD 制造商全稱:Analog Devices 功能描述:Microprocessor Supervisory Circuit |

發布緊急采購,3分鐘左右您將得到回復。