- 您現在的位置:買賣IC網 > PDF目錄374016 > ADN2811ACP-CML-RL (ANALOG DEVICES INC) OC-48/OC-48 FEC Clock and Data Recovery IC with Integrated Limiting Amp PDF資料下載

參數資料

| 型號: | ADN2811ACP-CML-RL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字傳輸電路 |

| 英文描述: | OC-48/OC-48 FEC Clock and Data Recovery IC with Integrated Limiting Amp |

| 中文描述: | CLOCK RECOVERY CIRCUIT, QCC48 |

| 封裝: | 7 X 7 MM, LEAD FREE, MO-220-VKKD-2, LFCSP-48 |

| 文件頁數: | 3/16頁 |

| 文件大小: | 359K |

| 代理商: | ADN2811ACP-CML-RL |

REV. A

ADN2811

–3–

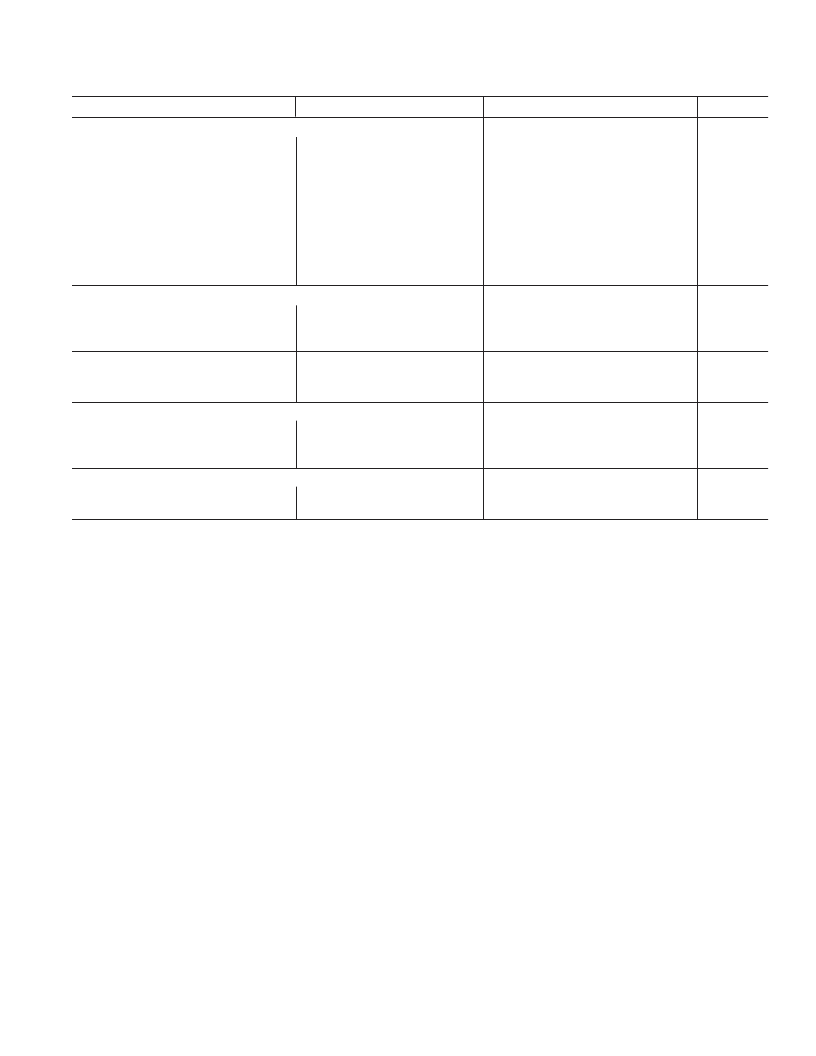

Parameter

Conditions

Min

Typ

Max

Unit

CML OUTPUTS (CLKOUTP/N, DATAOUTP/N)

Single-Ended Output Swing

Differential Output Swing

Output High Voltage

Output Low Voltage

Rise Time

Fall time

Setup Time

V

SE

(See Figure 3)

V

DIFF

(See Figure 3)

V

OH

V

OL

20%–80%

80%–20%

T

S

(See Figure 1)

OC-48

T

H

(See Figure 1)

OC-48

300

600

455

910

VCC

600

1200

mV

mV

V

V

ps

ps

VCC – 0.6

VCC – 0.3

150

150

84

84

140

ps

Hold Time

150

ps

REFCLK DC INPUT CHARACTERISTICS

Input Voltage Range

Peak-to-Peak Differential Input

Common-Mode Level

@ REFCLKP or REFCLKN

0

100

VCC

V

mV

V

DC-Coupled, Single-Ended

VCC/2

TEST DATA DC INPUT

CHARACTERISTICS

4

(TDINP/N)

Peak-to-Peak Differential Input Voltage

CML Inputs

0.8

V

LVTTL DC INPUT CHARACTERISTICS

Input High Voltage

Input Low Voltage

Input Current

V

IH

V

IL

V

IN

= 0.4 V or V

IN

= 2.4 V

2.0

V

V

0.8

+5

–5

LVTTL DC OUTPUT CHARACTERISTICS

Output High Voltage

Output Low Voltage

V

OH

, I

OH

= –2.0 mA

V

OL

, I

OL

= +2.0 mA

2.4

V

V

0.4

NOTES

1

PIN and NIN should be differentially driven, ac-coupled for optimum sensitivity.

2

PWD measurement made on quantizer outputs in BYPASS mode.

3

Measurement is equipment limited.

4

TDINP/N are CML inputs. If the drivers to the TDINP/N inputs are anything other than CML, they must be ac-coupled.

Specifications subject to change without notice.

相關PDF資料 |

PDF描述 |

|---|---|

| ADN2812 | Continuous Rate 12.3 Mb/s to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2812ACP | Continuous Rate 12.3 Mb/s to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2812ACP-RL | Continuous Rate 12.3 Mb/s to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2812ACP-RL7 | Continuous Rate 12.3 Mb/s to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2819 | Multirate to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADN2811ACPZ-CML | 功能描述:IC CLK/DATA REC W/AMP 48-LFCSP RoHS:是 類別:集成電路 (IC) >> 時鐘/計時 - 專用 系列:- 標準包裝:28 系列:- 類型:時鐘/頻率發生器 PLL:是 主要目的:Intel CPU 服務器 輸入:時鐘 輸出:LVCMOS 電路數:1 比率 - 輸入:輸出:3:22 差分 - 輸入:輸出:無/是 頻率 - 最大:400MHz 電源電壓:3.135 V ~ 3.465 V 工作溫度:0°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:64-TFSOP (0.240",6.10mm 寬) 供應商設備封裝:64-TSSOP 包裝:管件 |

| ADN2811ACPZ-CML-RL | 功能描述:IC CLK DATA REC SDH 2.66GHZ 制造商:analog devices inc. 系列:- 包裝:帶卷(TR) 零件狀態:上次購買時間 PLL:是 主要用途:SONET/SDH,STM 輸入:CML 輸出:CML 電路數:1 比率 - 輸入:輸出:1:2 差分 - 輸入:輸出:是/是 頻率 - 最大值:2.66GHz 電壓 - 電源:3 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-WFQFN 裸露焊盤 供應商器件封裝:48-LFCSP(7x7) 標準包裝:1 |

| ADN2812 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Continuous Rate 12.3 Mb/s to 2.7 Gb/s Clock and Data Recovery IC with Integrated Limiting Amp |

| ADN2812ACP | 制造商:Analog Devices 功能描述:IC CLOCK/DATA RECOVERY |

| ADN2812ACP-RL | 制造商:Analog Devices 功能描述:Clock and Data Recovery 32-Pin LFCSP EP T/R |

發布緊急采購,3分鐘左右您將得到回復。