- 您現在的位置:買賣IC網 > PDF目錄374017 > ADN2850ACP250-RL7 (ANALOG DEVICES INC) Nonvolatile Memory, Dual 1024 Position Programmable Resistors PDF資料下載

參數資料

| 型號: | ADN2850ACP250-RL7 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字電位計 |

| 英文描述: | Nonvolatile Memory, Dual 1024 Position Programmable Resistors |

| 中文描述: | DUAL 250K DIGITAL POTENTIOMETER, 3-WIRE SERIAL CONTROL INTERFACE, 1024 POSITIONS, QCC16 |

| 封裝: | 5 X 5 MM, LFCSP-16 |

| 文件頁數: | 6/18頁 |

| 文件大小: | 270K |

| 代理商: | ADN2850ACP250-RL7 |

PRELIMINARY TECHNICAL DATA

Nonvolatile Memory Programmable Resistors

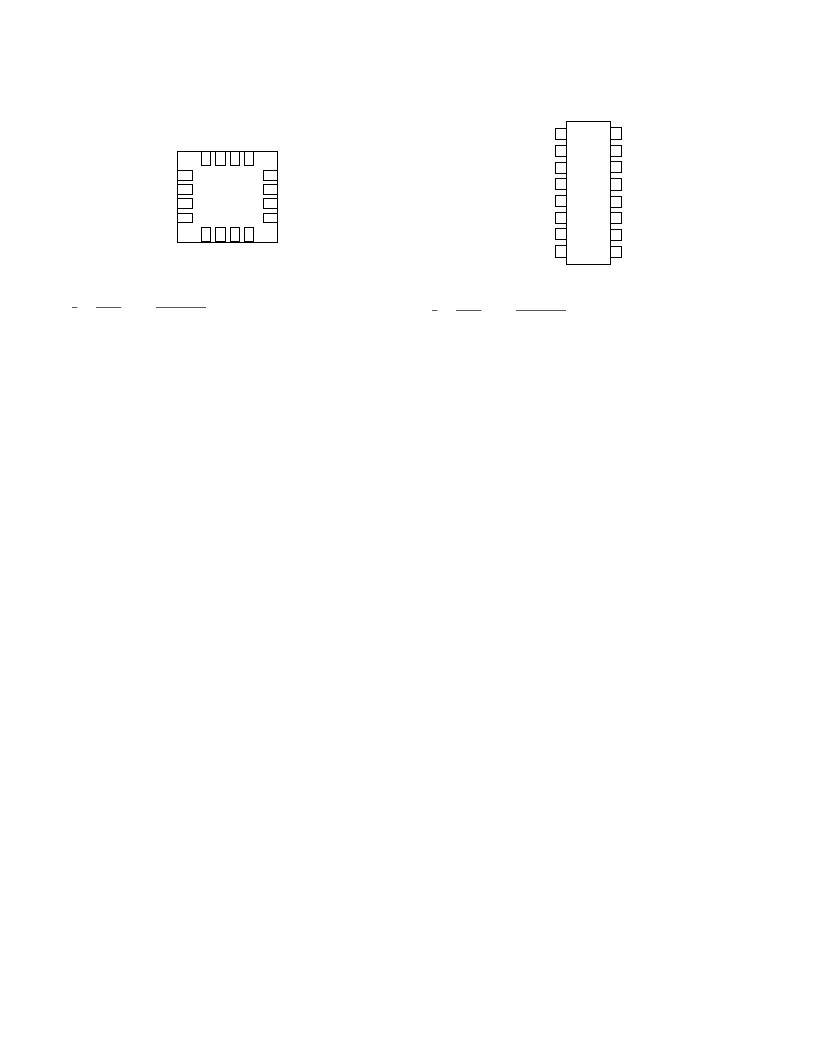

ADN2850ACP PIN CONFIGURATION

ADN2850

REV PrH, 13, AUG 2001

6

SDO

2

3

4

12

11

10

9

1

16

15

14

13

5

6

7

8

GND

V

SS

V

1

PR

WP

V

DD

V

2

W1

B1

B2

W2

SDI

CLK RDY

CS

ADN2850ACP PIN DESCRIPTION

#

1

Name

SDO

Description

Serial Data Output Pin. Open Drain Output requires

external pull-up resistor. Commands 9 and 10

activate the SDO output. See Instruction operation

Truth Table. Table 2. Other commands shift out the

previously loaded SDI bit pattern delayed by 24

clock pulses. This allows daisy-chain operation of

multiple packages.

Ground pin, logic ground reference

Negative Supply. Connect to zero volts for single

supply applications.

Log Output Voltage 1 generated from internal diode

configured transistor

Wiper terminal of RDAC1. ADDR(RDAC1) = 0

H

.

B terminal of RDAC1

B terminal of RDAC2.

Wiper terminal of RDAC2. ADDR(RDAC2) = 1

H

.

Log Output Voltage 2 generated from internal diode

configured transistor

Positive Power Supply Pin.

Write Protect Pin. When active low,

WP

prevents

any changes to the present register contents, except

PR

and cmd 1 and 8 will refresh the RDAC register

from EEMEM.

Hardware over ride preset pin. Refreshes the scratch

pad register with current contents of the EEMEM

register. Factory default loads midscale 512

10

until

EEMEM loaded with a new value by the user (

PR

is

activated at the logic high transition).

Serial Register chip select active low. Serial register

operation takes place when

CS

returns to logic high.

Ready. Active-high open drain output. Identifies

completion of commands 2, 3, 8, 9, 10, and

PR.

Serial Input Register clock pin. Shifts in one bit at a

time on positive clock edges.

Serial Data Input Pin. Shifts in one bit at a time on

positive clock CLK edges. MSB loaded first.

2

3

GND

V

SS

4

V

1

5

6

7

8

9

W1

B1

B2

W2

V

2

10

11

V

DD

WP

12

PR

13

CS

14

RDY

15

CLK

16

SDI

ADN2850ARU PIN CONFIGURATION

CLK

SDI

SDO

GND

V

SS

V

1

W1

B1

RDY

CS

PR

PR

WP

V

DD

V

2

W2

B2

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

ADN2850ARU PIN DESCRIPTION

#

1

Name

CLK

Description

Serial Input Register clock pin. Shifts in one bit at a

time on positive clock edges.

Serial Data Input Pin. Shifts in one bit at a time on

positive clock CLK edges. MSB loaded first.

Serial Data Output Pin. Open Drain Output requires

external pull-up resistor. Commands 9 and 10

activate the SDO output. See Instruction operation

Truth Table. Table 2. Other commands shift out the

previously loaded SDI bit pattern delayed by 24

clock pulses. This allows daisy-chain operation of

multiple packages

Ground pin, logic ground reference

Negative Supply. Connect to zero volts for single

supply applications.

Log Output Voltage 1 generated from internal diode

configured transistor

Wiper terminal of RDAC1. ADDR(RDAC1) = 0

H

.

B terminal of RDAC1

B terminal of RDAC2.

Wiper terminal of RDAC2. ADDR(RDAC2) = 1

H

.

Log Output Voltage 2 generated from internal diode

configured transistor

Positive Power Supply Pin.

Write Protect Pin. When active low,

WP

prevents

any changes to the present contents except

PR

and

cmd 1 and 8 will refresh the RDAC register from

E2MEM.

Hardware over ride preset pin. Refreshes the scratch

pad register with current contents of the EEMEM

register. Factory default loads midscale 512

10

until

EEMEM loaded with a new value by the user (

PR

is

activated at the logic high transition).

Serial Register chip select active low. Serial register

operation takes place when

CS

returns to logic high.

Ready. Active-high open drain output. Identifies

completion of commands 2, 3, 8, 9, 10, and

PR.

2

SDI

3

SDO

4

5

GND

V

SS

6

V

1

7

8

9

10

11

W1

B1

B2

W2

V

2

12

13

V

DD

WP

14

PR

15

CS

16

RDY

相關PDF資料 |

PDF描述 |

|---|---|

| ADN2860 | High Bandwidth, CMOS 8-Bit Serial Interface Multiplying D/A Converter; Package: MSOP; No of Pins: 10; Temperature Range: Industrial |

| ADN2870 | High Bandwidth, CMOS 8-Bit Serial Interface Multiplying D/A Converter; Package: MSOP; No of Pins: 10; Temperature Range: Industrial |

| ADN2870ACPZ | High Bandwidth, CMOS 8-Bit Serial Interface Multiplying D/A Converter; Package: MSOP; No of Pins: 10; Temperature Range: Industrial |

| ADN2870ACPZ-RL | 3.3 V Dual-Loop, 50 Mbps to 3.3 Gbps Laser Diode Driver |

| ADN2870ACPZ-RL7 | 3.3 V Dual-Loop, 50 Mbps to 3.3 Gbps Laser Diode Driver |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADN2850ACP25-RL7 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Nonvolatile Memory, Dual 1024 Position Programmable Resistors |

| ADN2850ARU | 制造商:Analog Devices 功能描述:DUAL 10-BIT PROGRAMMABLE NON-VOLATILE RESISTOR - Bulk |

| ADN2850ARU25 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Nonvolatile Memory, Dual 1024 Position Programmable Resistors |

| ADN2850ARU25-REEL7 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Nonvolatile Memory, Dual 1024 Position Programmable Resistors |

| ADN2850BCP25 | 制造商:Analog Devices 功能描述:Digital Potentiometer 1024POS 25KOhm Dual 16-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:DUAL 9-BIT SPI DIG. POT - Bulk |

發布緊急采購,3分鐘左右您將得到回復。