- 您現在的位置:買賣IC網 > PDF目錄374032 > ADSP-21062KS-133 (ANALOG DEVICES INC) ADSP-2106x SHARC DSP Microcomputer Family PDF資料下載

參數資料

| 型號: | ADSP-21062KS-133 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字信號處理 |

| 英文描述: | ADSP-2106x SHARC DSP Microcomputer Family |

| 中文描述: | 48-BIT, 33.33 MHz, OTHER DSP, PQFP240 |

| 封裝: | MS-029GA, MQFP-240 |

| 文件頁數: | 18/48頁 |

| 文件大小: | 370K |

| 代理商: | ADSP-21062KS-133 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

–18–

ADSP-21062/ADSP-21062L

REV. C

ADSP-21062

40 MHz

Min

Max

ADSP-21062L

40 MHz

Min

Max

33 MHz

Min

33 MHz

Min

Parameter

Max

Max

Units

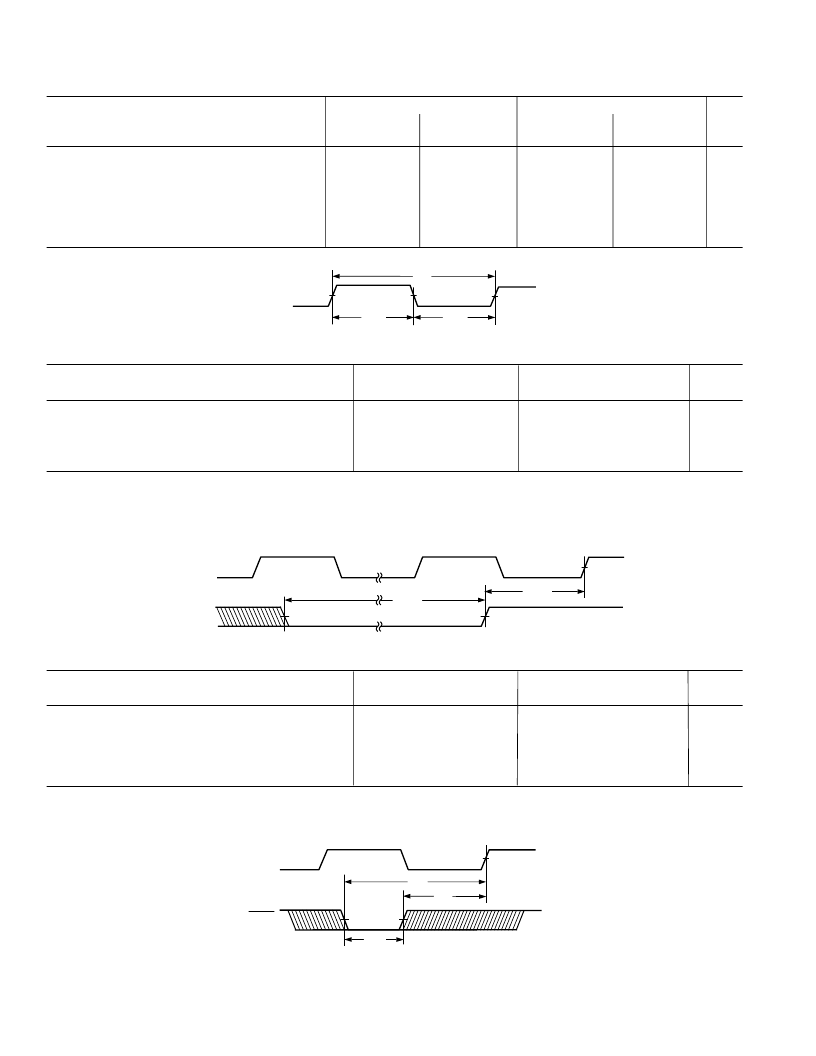

Clock Input

Timing Requirements:

t

CK

t

CKL

t

CKH

t

CKRF

CLKIN Period

CLKIN Width Low

CLKIN Width High

CLKIN Rise/Fall (0.4 V–2.0 V)

25

7

5

100

30

7

5

100

25

8.75

5

100

30

8.75

5

100

ns

ns

ns

ns

3

3

3

3

CLKIN

t

CKH

t

CK

t

CKL

Figure 8. Clock Input

ADSP-21062

Min

ADSP-21062L

Min

Parameter

Max

Max

Units

Reset

Timing Requirements:

t

WRST

t

SRST

RESET

Pulsewidth Low

1

RESET

Setup Before CLKIN High

2

4t

CK

14 + DT/2

4t

CK

14 + DT/2

ns

ns

t

CK

t

CK

NOTES

1

Applies after the power-up sequence is complete. At power-up, the processor’s internal phase-locked loop requires no more than 2000 CLKIN cycles while RESET

is low, assuming stable V

DD

and CLKIN (not including start-up time of external clock oscillator).

2

Only required if multiple ADSP-21062s must come out of reset synchronous to CLKIN with program counters (PC) equal (i.e., for a SIMD system). Not required

for multiple ADSP-21062s communicating over the shared bus (through the external port), because the bus arbitration logic synchronizes itself automatically after reset.

CLKIN

RESET

t

WRST

t

SRST

Figure 9. Reset

ADSP-21062

Min

ADSP-21062L

Min

Parameter

Max

Max

Units

Interrupts

Timing Requirements:

t

SIR

t

HIR

t

IPW

IRQ2-0

Setup Before CLKIN High

1

IRQ2-0

Hold Before CLKIN High

1

IRQ2-0

Pulsewidth

2

18 + 3DT/4

18 + 3DT/4

ns

ns

ns

12 + 3DT/4

12 + 3DT/4

2 + t

CK

2 + t

CK

NOTES

1

Only required for

IRQx

recognition in the following cycle.

2

Applies only if t

SIR

and t

HIR

requirements are not met.

CLKIN

IRQ2-0

t

IPW

t

SIR

t

HIR

Figure 10. Interrupts

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21062KS-160 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21062LKS-133 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21062LKS-160 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21062LCS-160 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21062LAB-160 | ADSP-2106x SHARC DSP Microcomputer Family |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP21062KS160 | 制造商:AD 功能描述:New |

| ADSP-21062KS-160 | 功能描述:IC DSP CONTROLLER 2MBIT 240MQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21062KSZ-133 | 功能描述:IC DSP CONTROLLER 32BIT 240MQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:40 系列:TMS320DM64x, DaVinci™ 類型:定點 接口:I²C,McASP,McBSP 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:160kB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:0°C ~ 90°C 安裝類型:表面貼裝 封裝/外殼:548-BBGA,FCBGA 供應商設備封裝:548-FCBGA(27x27) 包裝:托盤 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

| ADSP-21062KSZ-160 | 功能描述:IC DSP CONTROLLER 32BIT 240MQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21062L | 制造商:AD 制造商全稱:Analog Devices 功能描述:ADSP-2106x SHARC DSP Microcomputer Family |

發布緊急采購,3分鐘左右您將得到回復。