- 您現在的位置:買賣IC網 > PDF目錄374033 > ADSP-21266SKBCZ-2C (ANALOG DEVICES INC) SHARC Embedded Processor PDF資料下載

參數資料

| 型號: | ADSP-21266SKBCZ-2C |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字信號處理 |

| 英文描述: | SHARC Embedded Processor |

| 中文描述: | 16-BIT, 66.67 MHz, OTHER DSP, PBGA136 |

| 封裝: | ROHS COMPLIANT, MO-205AE, BGA-136 |

| 文件頁數: | 29/44頁 |

| 文件大小: | 426K |

| 代理商: | ADSP-21266SKBCZ-2C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

ADSP-21266

Rev. B

|

Page 29 of 44

|

May 2005

Serial Ports

To determine whether communication is possible between two

devices at clock speed n, the specifications in

Table 24

,

Table 25

,

Table 26

,

Table 27

,

Figure 21

, and

Figure 22

must be confirmed:

1) frame sync delay and frame sync setup and hold; 2) data delay

and data setup and hold; and 3) SCLK width.

Serial port signals (SCLK, FS, DxA,/DxB) are routed to the

DAI_P20

–

1 pins using the SRU. Therefore, the timing specifi-

cations provided below are valid at the DAI_P20

–

1 pins.

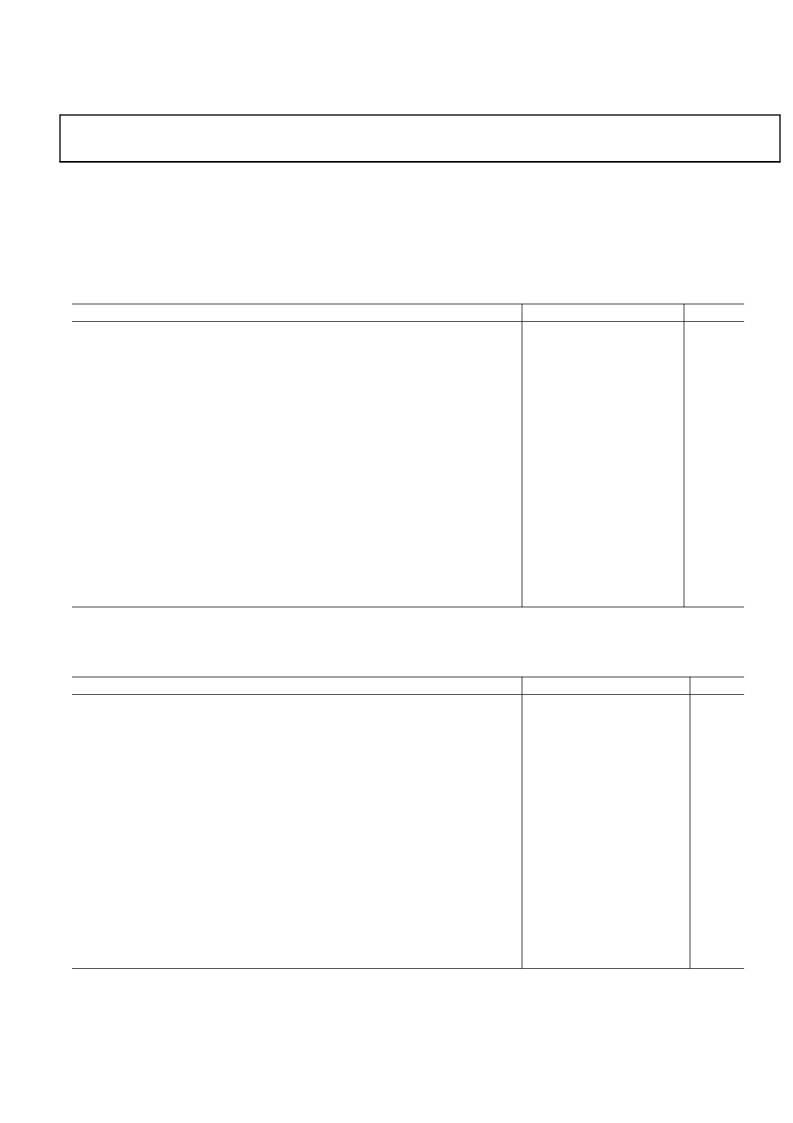

Table 24. Serial Ports—External Clock

Parameter

Timing Requirements

t

SFSE

Min

Max

Unit

FS Setup Before SCLK

(Externally Generated FS in Either Transmit or Receive Mode)

1

FS Hold After SCLK

(Externally Generated FS in Either Transmit or Receive Mode)

1

Receive Data Setup Before Receive SCLK

1

Receive Data Hold After SCLK

1

SCLK Width

SCLK Period

2.5

ns

t

HFSE

2.5

2.5

2.5

7

20

ns

ns

ns

ns

ns

t

SDRE

t

HDRE

t

SCLKW

t

SCLK

Switching Characteristics

t

DFSE

FS Delay After SCLK

(Internally Generated FS in Either Transmit or Receive Mode)

2

FS Hold After SCLK

(Internally Generated FS in Either Transmit or Receive Mode)

2

Transmit Data Delay After Transmit SCLK

2

Transmit Data Hold After Transmit SCLK

2

7

ns

t

HOFSE

2

ns

ns

ns

t

DDTE

t

HDTE

7

2

1

Referenced to sample edge.

2

Referenced to drive edge.

Table 25. Serial Ports—Internal Clock

Parameter

Timing Requirements

t

SFSI

Min

Max

Unit

FS Setup Before SCLK

(Externally Generated FS in Either Transmit or Receive Mode)

1

FS Hold After SCLK

(Externally Generated FS in Either Transmit or Receive Mode)

1

Receive Data Setup Before SCLK

1

Receive Data Hold After SCLK

1

6

ns

t

HFSI

1.5

6

1.5

ns

ns

ns

t

SDRI

t

HDRI

Switching Characteristics

t

DFSI

t

HOFSI

t

DFSI

t

HOFSI

t

DDTI

t

HDTI

t

SCLKIW

FS Delay After SCLK (Internally Generated FS in Transmit Mode)

2

FS Hold After SCLK (Internally Generated FS in Transmit Mode)

2

FS Delay After SCLK (Internally Generated FS in Receive Mode)

2

FS Hold After SCLK (Internally Generated FS in Receive Mode)

2

Transmit Data Delay After SCLK

2

Transmit Data Hold After SCLK

2

Transmit or Receive SCLK Width

3

ns

ns

ns

ns

ns

ns

ns

–1.0

3

–1.0

3

–1.0

0.5t

SCLK

– 2

0.5t

SCLK

+ 2

1

Referenced to the sample edge.

2

Referenced to drive edge.

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21266SKBCZ-2D | SHARC Embedded Processor |

| ADSP-21266SKSTZ-1B | SHARC Embedded Processor |

| ADSP-21266SKSTZ-1C | SHARC Embedded Processor |

| ADSP-21266SKSTZ-2B | SHARC Embedded Processor |

| ADSP-21266SKSTZ-2C | SHARC Embedded Processor |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-21266SKBCZ-2D | 功能描述:IC DSP 32BIT 200MHZ 136-CSPBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21266SKSTZ-1B | 制造商:Analog Devices 功能描述: 制造商:Analog Devices 功能描述:DSP FLOATING PT 32BIT 150MHZ 150MIPS 144LQFP - Trays |

| ADSP-21266SKSTZ-1C | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit 150MHz 150MIPS 144-Pin LQFP 制造商:Analog Devices 功能描述:DSP FLOATING PT 32BIT 150MHZ 150MIPS 144LQFP - Trays |

| ADSP-21266SKSTZ-1D | 功能描述:IC DSP 32BIT 150MHZ 144-LQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21266SKSTZ-2B | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit 200MHz 200MIPS 144-Pin LQFP |

發布緊急采購,3分鐘左右您將得到回復。