- 您現在的位置:買賣IC網 > PDF目錄374033 > ADSP-21364SKBCZENG (ANALOG DEVICES INC) SHARC Processor PDF資料下載

參數資料

| 型號: | ADSP-21364SKBCZENG |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字信號處理 |

| 英文描述: | SHARC Processor |

| 中文描述: | 16-BIT, 55.55 MHz, OTHER DSP, PBGA136 |

| 封裝: | LEAD FREE, MO-205AE, MBGA-136 |

| 文件頁數: | 18/52頁 |

| 文件大小: | 853K |

| 代理商: | ADSP-21364SKBCZENG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

Rev. PrB

|

Page 18 of 52

|

September 2004

ADSP-21364

Preliminary Technical Data

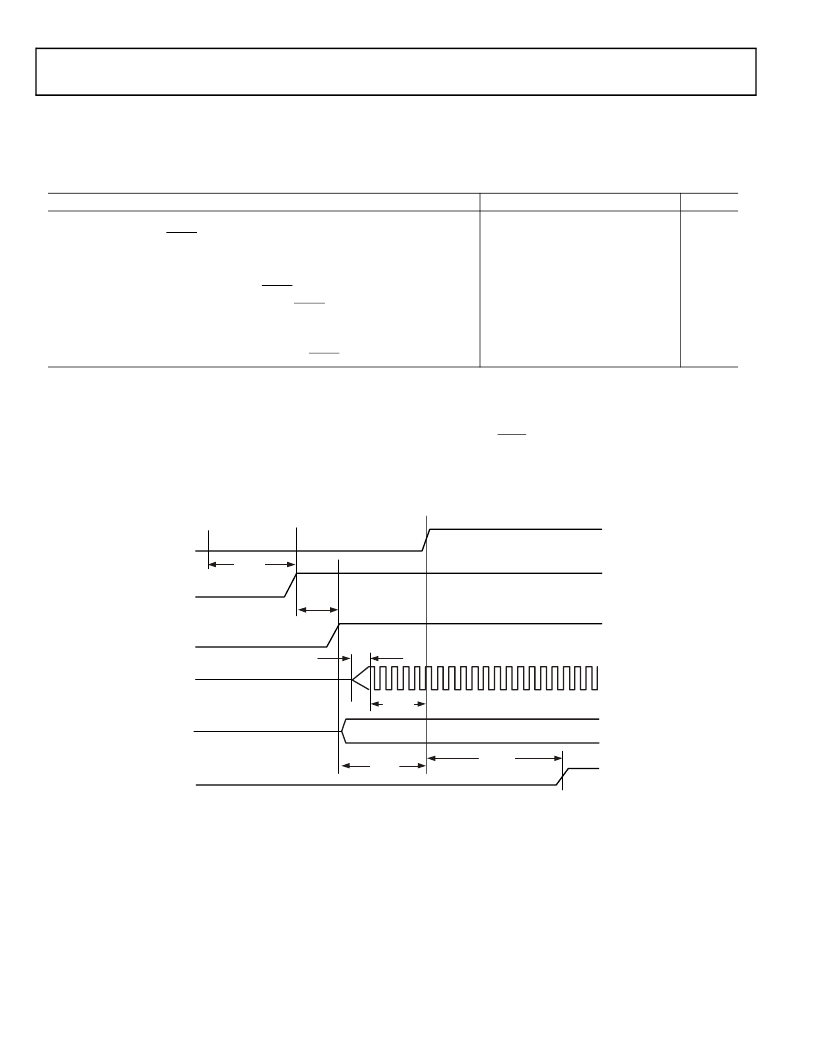

Power-Up Sequencing

The timing requirements for processor startup are given in

Table 10

.

Table 10. Power-Up Sequencing Timing Requirements (Processor Startup)

Parameter

Timing Requirements

t

RSTVDD

t

IVDDEVDD

t

CLKVDD

1

t

CLKRST

t

PLLRST

Min

Max

Unit

RESET Low Before V

DDINT

/V

DDEXT

on

V

DDINT

on Before V

DDEXT

CLKIN Valid After V

DDINT

/V

DDEXT

Valid

CLKIN Valid Before RESET Deasserted

PLL Control Setup Before RESET Deasserted

0

–50

0

10

2

20

3

ns

ms

ms

μs

μs

200

200

Switching Characteristic

t

CORERST

1

Valid V

DDINT

/V

DDEXT

assumes that the supplies are fully ramped to their 1.2 and 3.3 volt rails. Voltage ramp rates can vary from microseconds to hundreds of milliseconds

depending on the design of the power supply subsystem.

2

Assumes a stable CLKIN signal, after meeting worst-case startup timing of crystal oscillators. Refer to your crystal oscillator manufacturer's datasheet for startup time.

Assume a 25 ms maximum oscillator startup time if using the XTAL pin and internal oscillator circuit in conjunction with an external crystal.

3

Based on CLKIN cycles

4

Applies after the power-up sequence is complete. Subsequent resets require a minimum of 4 CLKIN cycles for RESET to be held low in order to properly initialize and

propagate default states at all I/O pins.

5

The 4096 cycle count depends on t

SRST

specification in

Table 12

. If setup time is not met, 1 additional CLKIN cycle may be added to the core reset time, resulting in 4097

cycles maximum.

Core Reset Deasserted After RESET Deasserted

4096t

CK

+ 2 t

CCLK

4, 5

Figure 6. Power Up Sequencing

CLKIN

RESET

RSTOUT

VDDEXT

VDDINT

t

PLLRST

t

CLKRST

t

CLKVDD

t

IVDDEVDD

CLK_CFG1-0

t

CORERST

t

RSTVDD

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21364SKSQ-ENG | SHARC Processor |

| ADSP-21364SKSQZENG | SHARC Processor |

| ADSP-21365SKBC-ENG | SHARC Processor |

| ADSP-21365SBSQZENG | SHARC Processor |

| ADSP-21365SCSQ-ENG | SHARC Processor |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-21364SKSQ-ENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21364SKSQZENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21364WBBCZ-1A | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21364YSWZ-2AA | 功能描述:IC DSP 32BIT 200MHZ EPAD 144LQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21365 | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

發布緊急采購,3分鐘左右您將得到回復。