- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374034 > ADSP-21365SKSQZENG (ANALOG DEVICES INC) SHARC Processor PDF資料下載

參數(shù)資料

| 型號: | ADSP-21365SKSQZENG |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | SHARC Processor |

| 中文描述: | 16-BIT, 55.55 MHz, OTHER DSP, PQFP144 |

| 封裝: | LEAD FREE, MS-026BFB-HD, HSLQFP-144 |

| 文件頁數(shù): | 25/54頁 |

| 文件大小: | 559K |

| 代理商: | ADSP-21365SKSQZENG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

ADSP-21365/6

Preliminary Technical Data

Rev. PrA

|

Page 25 of 54

|

September 2004

Memory Read—Parallel Port

Use these specifications for asynchronous interfacing to memo-

ries (and memory-mapped peripherals) when the

ADSP-21365/6 is accessing external memory space.

Table 20. 8-Bit Memory Read Cycle

Parameter

Timing Requirements

t

DRS

t

DRH

t

DAD

Min

Max

Unit

Address/Data 7–0 Setup Before RD High

Address/Data 7–0 Hold After RD High

Address 15–8 to Data Valid

3.3

0

ns

ns

ns

D + t

PCLK

– 5

Switching Characteristics

t

ALEW

t

ADAS

1

t

RRH

t

ALERW

t

RWALE

t

ADAH

1

t

ALEHZ

1

t

RW

t

RDDRV

t

ADRH

D = (Data Cycle Duration = the value set by the PPDUR bits (5–1) in the PPCTL register) × t

PCLK

H = t

PCLK

(if a hold cycle is specified, else H = 0)

F = 7 x t

PCLK

(if FLASH_MODE is set else F = 0)

t

PCLK

= (Peripheral) Clock Period = 2 × t

CCLK

1

On reset, ALE is an active high cycle. However, it can be configured by software to be active low.

ALE Pulse Width

Address/Data 15–0 Setup Before ALE Deasserted

Delay Between RD Rising Edge to Next Falling Edge.

ALE Deasserted to Read Asserted

Read Deasserted to ALE Asserted

Address/Data 15–0 Hold After ALE Deasserted

ALE Deasserted to Address/Data7–0 in High Z

RD Pulse Width

RD Address Drive After Read High

Address/Data 15–8 Hold After RD High

2 × t

PCLK

– 2.0

t

PCLK

– 2.5

H + t

PCLK

– 1

2 × t

PCLK

– 2

F + H + 0.5

t

PCLK

– 0.8

t

PCLK

– 0.8

D – 2

F + H + t

PCLK

– 1

H

ns

ns

ns

ns

ns

t

PCLK

ns

ns

ns

ns

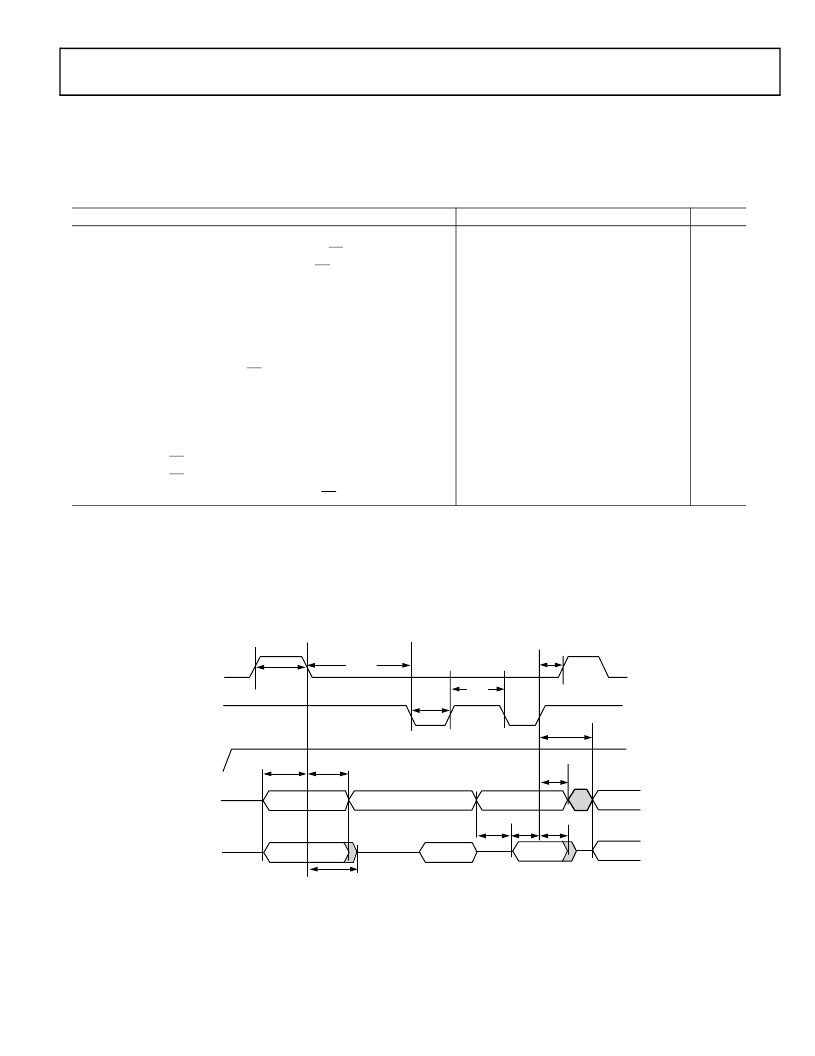

Figure 17. Read Cycle For 8-Bit Memory Timing

VALID ADDRESS

VALID

ADDRESS

AD15-8

t

ADAS

VALID ADDRESS

AD7-0

t

ALEW

ALE

RD

t

RW

WR

t

ADAH

t

ADRH

t

DRS

t

DRH

t

DAD

t

ALERW

t

RWALE

VALID

DATA

VALID

ADDRESS

t

RDDRV

t

ALEHZ

VALID ADDRESS

VALID ADDRESS

VALID

DATA

t

RRH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-21366SKBCZENG | SHARC Processor |

| ADSP-21366SBBCZENG | SHARC Processor |

| ADSP-21366SBSQZENG | SHARC Processor |

| ADSP-21366SCSQZENG | SHARC Processor |

| ADSP-21366SKSQ-ENG | SHARC Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-21365YSWZ-2AA | 功能描述:IC DSP 32BIT 200MHZ EPAD 144LQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數(shù)字式信號處理器) 系列:SHARC® 標(biāo)準(zhǔn)包裝:2 系列:StarCore 類型:SC140 內(nèi)核 接口:DSI,以太網(wǎng),RS-232 時鐘速率:400MHz 非易失內(nèi)存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21365YSWZ-2BA | 制造商:Analog Devices 功能描述:DSP Floating-Point 32-Bit/40-Bit 200MHz 200MIPS 144-Pin LQFP EP |

| ADSP-21365YSWZ-2CA | 功能描述:IC DSP 32BIT 200MHZ EPAD 144LQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數(shù)字式信號處理器) 系列:SHARC® 標(biāo)準(zhǔn)包裝:2 系列:StarCore 類型:SC140 內(nèi)核 接口:DSI,以太網(wǎng),RS-232 時鐘速率:400MHz 非易失內(nèi)存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21366 | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21366BBC-1AA | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 333 MHz SHARC with on chipRom RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。