- 您現在的位置:買賣IC網 > PDF目錄374035 > ADSP-2172 (Analog Devices, Inc.) DSP Microcomputer(DSP 微計算機) PDF資料下載

參數資料

| 型號: | ADSP-2172 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | DSP Microcomputer(DSP 微計算機) |

| 中文描述: | 微機的DSP(數字信號處理器微計算機) |

| 文件頁數: | 1/52頁 |

| 文件大小: | 685K |

| 代理商: | ADSP-2172 |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

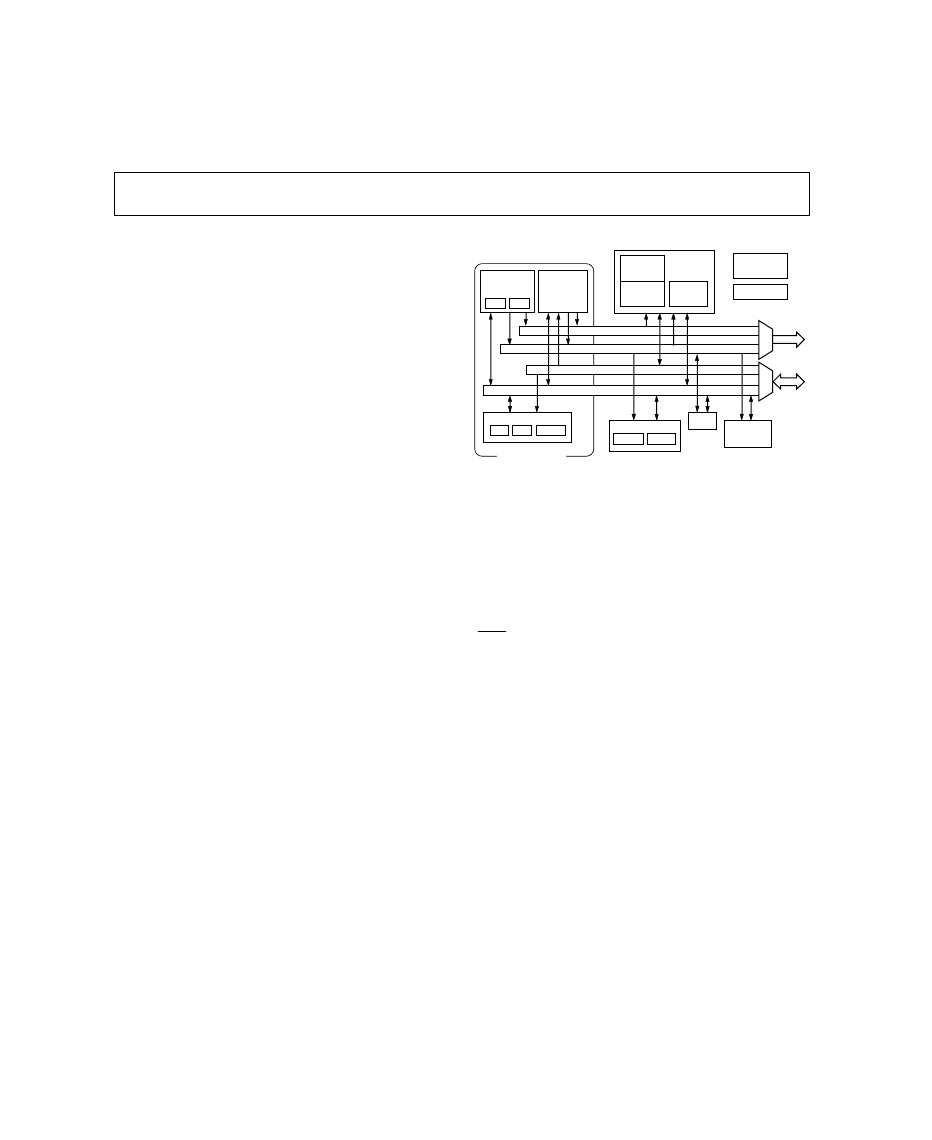

FUNCT IONAL BLOCK DIAGRAM

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

DSP Mcrocomputer

T he ADSP-217x combines the ADSP-2100 base architecture

(three computational units, data address generators, and a pro-

gram sequencer) with two serial ports, a host interface port, a

programmable timer, extensive interrupt capabilities, and on-

chip program and data memory.

In addition, the ADSP-217x supports new instructions, which

include bit manipulations–bit set, bit clear, bit toggle, bit test–

new ALU constants, new multiplication instruction (x squared),

biased rounding, and global interrupt masking, for increased

flexibility. T he ADSP-217x also has a Bus Grant Hang Logic

(

BGH

) feature.

T he ADSP-217x provides 2K words (24-bit) of program RAM

and 2K words (16-bit) of data memory. T he ADSP-2172 pro-

vides an additional 8K words (24-bit) of program ROM. Power-

down circuitry is also provided to meet the low power needs of

battery operated portable equipment. T he ADSP-217x is avail-

able in 128-pin T QFP and 128-pin PQFP packages.

Fabricated in a high-speed, double metal, low power, CMOS

process, the ADSP-217X operates with a 30 ns instruction cycle

time. Every instruction can execute in a single processor cycle.

T he ADSP-217x’s flexible architecture and comprehensive in-

struction set allow the processor to perform multiple operations

in parallel. In one processor cycle the ADSP-217x can:

generate the next program address

fetch the next instruction

perform one or two data moves

update one or two data address pointers

perform a computational operation

T his takes place while the processor continues to:

receive and transmit data through the two serial ports

receive and/or transmit data through the host interface port

decrement timer

FEATURES

30 ns Instruction Cycle Time (33 MIPS) from

16.67 MHz Crystal at 5.0 V

50 ns Instruction Cycle Time (20 MIPS) from 10 MHz

Crystal at 3.3 V

ADSP-2100 Family Code & Function Compatible with

New Instruction Set Enhancements for Bit Manipula-

tion Instructions, Multiplication Instructions, Biased

Rounding, and Global Interrupt Masking

Bus Grant Hang Logic

2K Words of On-Chip Program Memory RAM

2K Words of On-Chip Data Memory RAM

8K Words of On-Chip Program Memory ROM

(ADSP-2172)

8- or 16-Bit Parallel Host Interface Port

300 mW Typical Power Dissipation at 5.0 V at 30 ns

70 mW Typical Power Dissipation at 3.3 V at 50 ns

Powerdown Mode Featuring Less than 0.55 mW (ADSP-

2171/ADSP-2172) or 0.36 mW (ADSP-2173) CMOS

Standby Power Dissipation with 100 Cycle Recovery

from Powerdown

Dual Purpose Program Memory for Both Instruction

and Data Storage

Independent ALU, Multiplier/Accumulator, and Barrel

Shifter Computational Units

Two Independent Data Address Generators

Powerful Program Sequencer Provides

Zero Overhead Looping

Conditional Instruction Execution

Two Double-Buffered Serial Ports with Companding

Hardware and Automatic Data Buffering

Programmable 16-Bit Interval Timer with Prescaler

Programmable Wait State Generation

Automatic Booting of Internal Program Memory from

Byte-Wide External Memory, e.g., EPROM, or

Through Host Interface Port

Stand-Alone ROM Execution (Optional)

Single-Cycle Instruction Execution

Single-Cycle Context Switch

Multifunction Instructions

Three Edge- or Level-Sensitive External Interrupts

Low Power Dissipation in Standby Mode

128-Lead TQFP and 128-Lead PQFP

GE NE RAL DE SCRIPT ION

T he ADSP-2171, ADSP-2172, and ADSP-2173 are single-chip

microcomputers optimized for digital signal processing (DSP)

and other high-speed numeric processing applications. T he

ADSP-2171 and ADSP-2172 are designed for 5.0 V applica-

tions. T he ADSP-2173 is designed for 3.3 V applications. T he

ADSP-2172 also has 8K words (24-bit) of program ROM.

Analog Devices, Inc., 1995

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700

Fax: 617/326-8703

EXTERNAL

ADDRESS

BUS

EXTERNAL

DATA

BUS

ARITHMETIC UNITS

SHIFTER

MAC

ALU

MEMORY

SERIAL PORTS

SPORT 0

SPORT 1

FLAGS

GADATA

DAG 1

DAG 2

PROGRAM

PROGRAM MEMORY ADDRESS

DATA MEMORY ADDRESS

DATA MEMORY DATA

TIMER

PROGRAM MEMORY DATA

2K x 16

PRROM

8K x 24

PRRAM

2K x 24

PCONTROL

LOGIC

IN PORT

ADSP-2100 BASE

ARCHITECTURE

ADSP-2171/ADSP-2172/ADSP-2173

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-2173 | DSP Microcomputer(DSP 微計算機) |

| ADSP-2181BS-115 | DSP Microcomputer |

| ADSP-2181BS-133 | DSP Microcomputer |

| ADSP-2181KS-115 | DSP Microcomputer |

| ADSP-2181KS-133 | DSP Microcomputer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-2173 | 制造商:AD 制造商全稱:Analog Devices 功能描述:DSP Microcomputer |

| ADSP-2173BS-80 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADSP-2173BST-80 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 20MHz 20MIPS 128-Pin TQFP 制造商:Rochester Electronics LLC 功能描述:16BIT FXD PT PROC 3.3V - Bulk |

| ADSP-2176-760040 | 制造商:Analog Devices 功能描述: |

| ADSP-2176-760061 | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。