- 您現在的位置:買賣IC網 > PDF目錄374036 > ADSP-2186BST-133 (ANALOG DEVICES INC) DSP Microcomputer PDF資料下載

參數資料

| 型號: | ADSP-2186BST-133 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字信號處理 |

| 英文描述: | DSP Microcomputer |

| 中文描述: | 24-BIT, 16.67 MHz, OTHER DSP, PQFP100 |

| 封裝: | METRIC, PLASTIC, TQFP-100 |

| 文件頁數: | 10/36頁 |

| 文件大小: | 237K |

| 代理商: | ADSP-2186BST-133 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

ADSP-2186

–10–

REV. A

The IDMA port has a 16-bit multiplexed address and data bus

and supports 24-bit program memory. The IDMA port is com-

pletely asynchronous and can be written to while the ADSP-

2186 is operating at full speed.

The DSP memory address is latched and then automatically

incremented after each IDMA transaction. An external device

can therefore access a block of sequentially addressed memory

by specifying only the starting address of the block. This in-

creases throughput as the address does not have to be sent for

each memory access.

IDMA Port access occurs in two phases. The first is the IDMA

Address Latch cycle. When the acknowledge is asserted, a 14-bit

address and 1-bit destination type can be driven onto the bus by

an external device. The address specifies an on-chip memory

location, the destination type specifies whether it is a DM or

PM access. The falling edge of the address latch signal latches

this value into the IDMAA register.

Once the address is stored, data can then either be read from or

written to the ADSP-2186’s on-chip memory. Asserting the

select line (

IS

) and the appropriate read or write line (

IRD

and

IWR

respectively) signals the ADSP-2186 that a particular

transaction is required. In either case, there is a one-processor-

cycle delay for synchronization. The memory access consumes

one additional processor cycle.

Once an access has occurred, the latched address is automati-

cally incremented and another access can occur.

Through the IDMAA register, the DSP can also specify the

starting address and data format for DMA operation.

Bootstrap Loading (Booting)

The ADSP-2186 has two mechanisms to allow automatic load-

ing of the internal program memory after reset. The method for

booting is controlled by the Mode A, B and C configuration bits

as shown in Table VI. These four states can be compressed into

two-state bits by allowing an IDMA boot with Mode C = 1.

However, three bits are used to ensure future compatibility with

parts containing internal program memory ROM.

BDMA Booting

When the MODE pins specify BDMA booting, the ADSP-2186

initiates a BDMA boot sequence when

RESET

is released.

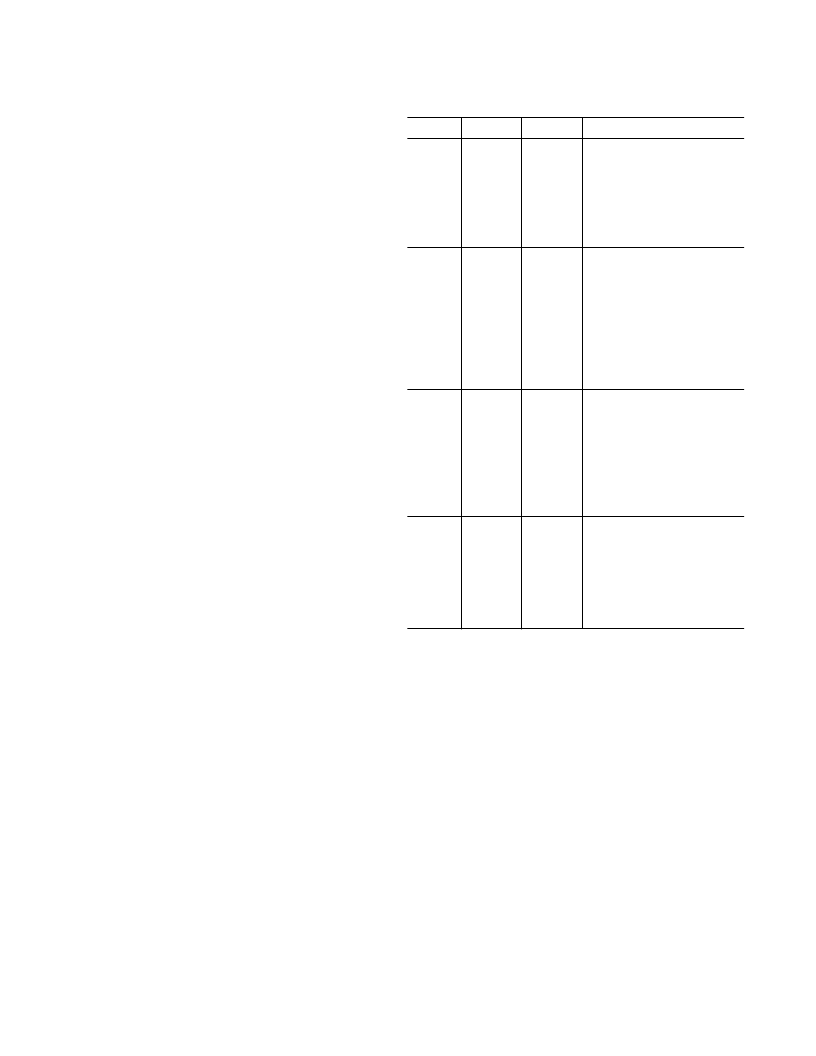

Table VI. Boot Summary Table

MODE C MODE B MODE A Booting Method

0

0

0

BDMA feature is used to load

the first 32 program memory

words from the byte memory

space. Program execution is

held off until all 32 words have

been loaded. Chip is config-

ured in Full Memory Mode.

0

1

0

No Automatic boot operations

occur. Program execution

starts at external memory

location 0. Chip is configured

in Full Memory Mode.

BDMA can still be used but

the processor does not auto-

matically use or wait for these

operations.

1

0

0

BDMA feature is used to load

the first 32 program memory

words from the byte memory

space. Program execution is

held off until all 32 words have

been loaded. Chip is config-

ured in Host Mode. Additional

interface hardware is required.

1

0

1

IDMA feature is used to load

any internal memory as de-

sired. Program execution is

held off until internal program

memory location 0 is written

to. Chip is configured in Host

Mode.

The BDMA interface is set up during reset to the following de-

faults when BDMA booting is specified: the BDIR, BMPAGE,

BIAD and BEAD registers are set to 0; the BTYPE register is

set to 0 to specify program memory 24-bit words; and the

BWCOUNT register is set to 32. This causes 32 words of on-

chip program memory to be loaded from byte memory. These

32 words are used to set up the BDMA to load in the remaining

program code. The BCR bit is also set to 1, which causes pro-

gram execution to be held off until all 32 words are loaded into

on-chip program memory. Execution then begins at address 0.

The ADSP-2100 Family development software (Revision 5.02

and later) fully supports the BDMA booting feature and can

generate byte memory space compatible boot code.

The IDLE instruction can also be used to allow the processor

to hold off execution while booting continues through the

BDMA interface. For BDMA accesses while in Host Mode,

the addresses to boot memory must be constructed externally

to the ADSP-2186. The only memory address bit provided by

the processor is A0.

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-2186BST-160 | DSP Microcomputer |

| ADSP-2186KST-115 | DSP Microcomputer |

| ADSP-2186KST-133 | DSP Microcomputer |

| ADSP-2186KST-160 | DSP Microcomputer |

| ADSP-2186LBCA-160 | DSP Microcomputer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-2186BST-133R | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 33.3MHz 33.3MIPS 100-Pin LQFP T/R |

| ADSP-2186BST-160 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 40MHz 40MIPS 100-Pin LQFP |

| ADSP-2186BST-160X | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Digital Signal Processor |

| ADSP-2186BSTZ-115 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 28.8MHz 28.8MIPS 100-Pin LQFP 制造商:Rochester Electronics LLC 功能描述: |

| ADSP-2186BSTZ-133 | 制造商:AD 制造商全稱:Analog Devices 功能描述:DSP Microcomputer |

發布緊急采購,3分鐘左右您將得到回復。