- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374037 > ADSP-2195MKCA-160X (ANALOG DEVICES INC) DSP Microcomputer PDF資料下載

參數(shù)資料

| 型號: | ADSP-2195MKCA-160X |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | DSP Microcomputer |

| 中文描述: | 16-BIT, 160 MHz, OTHER DSP, PBGA144 |

| 封裝: | MINI, BGA-144 |

| 文件頁數(shù): | 8/68頁 |

| 文件大小: | 951K |

| 代理商: | ADSP-2195MKCA-160X |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

For current information contact Analog Devices at 800/262-5643

ADSP-2195

September 2001

This information applies to a product under development. Its characteristics and specifications are subject to change with-

out notice. Analog Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing.

8

REV. PrA

External (Off-Chip) Memory

Each of the ADSP-2195’s off-chip memory spaces has a

separate control register, so applications can configure

unique access parameters for each space. The access param-

eters include read and write wait counts, waitstate

completion mode, I/O clock divide ratio, write hold time

extension, strobe polarity, and data bus width. The core

clock and peripheral clock ratios influence the external

memory access strobe widths.

For more information, see

Clock Signals on page 14.

The off-chip memory spaces are:

External memory space (MS3–0 pins)

I/O memory space (IOMS pin)

Boot memory space (BMS pin)

All of these off-chip memory spaces are accessible through

the External Port, which can be configured for 8-bit or

16-bit data widths.

External Memory Space

External memory space consists of four memory banks.

These banks can contain a configurable number of 64K

word pages. At reset, the page boundaries for external

memory have Bank0 containing pages 1

63, Bank1 con-

taining pages 64

127, Bank2 containing pages 128

191,

and Bank3 containing Pages 192

254. The MS3–0

memory bank pins select Banks 3–0, respectively. The

external memory interface decodes the 8 MSBs of the DSP

program address to select one of the four banks. Both the

ADSP-219x core and DMA-capable peripherals can access

the DSP’s external memory space.

I/O Memory Space

The ADSP-2195 supports an additional external memory

called I/O memory space. This space is designed to support

simple connections to peripherals (such as data converters

and external registers) or to bus interface ASIC data regis-

ters. I/O space supports a total of 256K locations. The first

8K addresses are reserved for on-chip peripherals. The

upper 248K addresses are available for external peripheral

devices. The DSP’s instruction set provides instructions for

accessing I/O space. These instructions use an 18-bit

address that is assembled from an 8-bit I/O page (IOPG)

register and a 10-bit immediate value supplied in the

instruction. Both the ADSP-219x core and a Host (through

the Host Port Interface) can access I/O memory space.

Boot Memory Space

Boot memory space consists of one off-chip bank with 254

pages. The BMS memory bank pin selects boot memory

space. Both the ADSP-219x core and DMA-capable

peripherals can access the DSP’s off-chip boot memory

space. After reset, the DSP always starts executing instruc-

tions from the on-chip boot ROM. Depending on the boot

configuration, the boot ROM code can start booting the

DSP from boot memory.

For more information, see Booting

Modes on page 15.

Interrupts

The interrupt controller lets the DSP respond to 17 inter-

rupts with minimum overhead. The controller implements

an interrupt priority scheme as shown in

Table 1

. Applica-

tions can use the unassigned slots for software and

peripheral interrupts.

Table 2

shows the ID and priority at reset of each of the

peripheral interrupts. To assign the peripheral interrupts a

different priority, applications write the new priority to their

corresponding control bits (determined by their ID) in the

Interrupt Priority Control register. The peripheral inter-

rupt’s position in the IMASK and IRPTL register and its

vector address depend on its priority level, as shown in

Table 1

. Because the IMASK and IRPTL registers are

limited to 16 bits, any peripheral interrupts assigned a

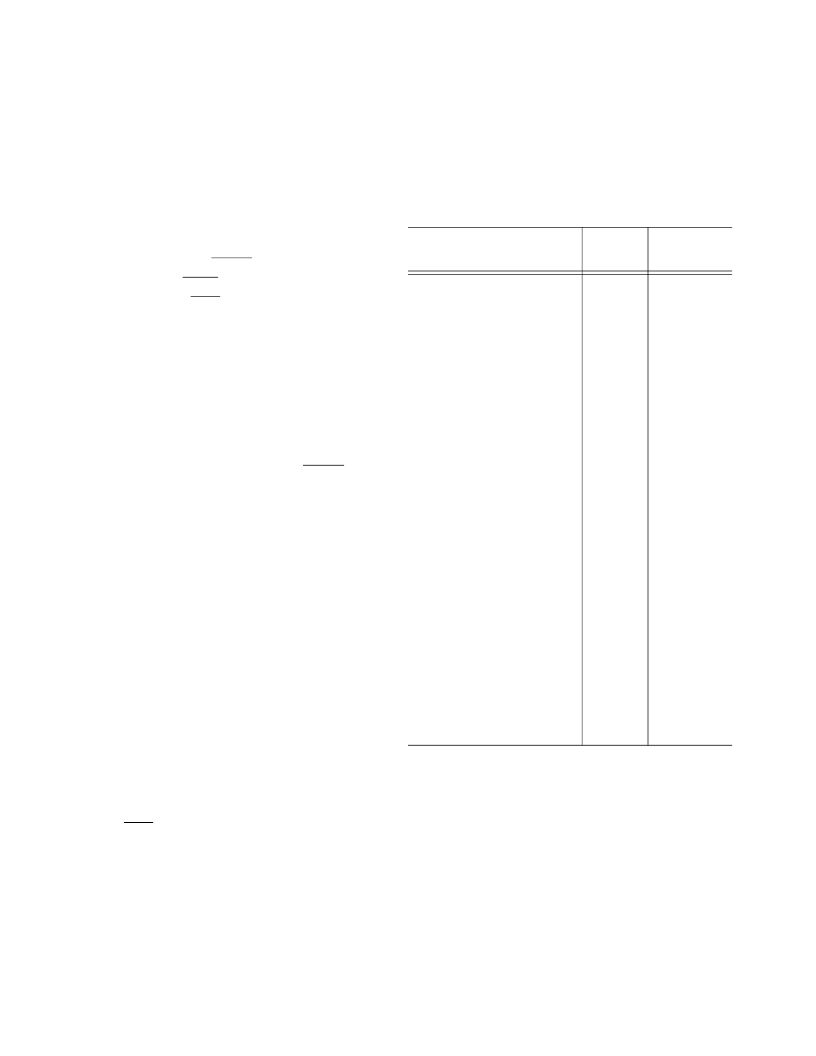

Table 1. Interrupt Priorities/Addresses

Interrupt

IMASK/

IRPTL

Vector

Address

1

1

These interrupt vectors start at address 0x10000 when the DSP is in

“no-boot”, run-form-external memory mode.

Emulator (NMI)—

Highest Priority

NA

NA

Reset (NMI)

0

0x00 0000

Power-Down (NMI)

1

0x00 0020

Loop and PC Stack

2

0x00 0040

Emulation Kernel

3

0x00 0060

User Assigned Interrupt

4

0x00 0080

User Assigned Interrupt

5

0x00 00A0

User Assigned Interrupt

6

0x00 00C0

User Assigned Interrupt

7

0x00 00E0

User Assigned Interrupt

8

0x00 0100

User Assigned Interrupt

9

0x00 0120

User Assigned Interrupt

10

0x00 0140

User Assigned Interrupt

11

0x00 0160

User Assigned Interrupt

12

0x00 0180

User Assigned Interrupt

13

0x00 01A0

User Assigned Interrupt

14

0x00 01C0

User Assigned Interrupt—

Lowest Priority

15

0x00 01E0

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-2195MBST-140X | DSP Microcomputer |

| ADSP-2195 | LM2991 Negative Low Dropout Adjustable Regulator; Package: CERDIP; No of Pins: 16; Qty per Container: 25; Container: Rail |

| ADSP-2195MBCA-140X | LM2991 Negative Low Dropout Adjustable Regulator; Package: CERDIP; No of Pins: 16; Container: Rail |

| ADSP-2195MKST-160X | LM2991 Negative Low Dropout Adjustable Regulator; Package: TO-263; No of Pins: 5; Qty per Container: 45; Container: Rail |

| ADSP-2196 | DSP Microcomputer |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2195MKST-160 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 24-Bit 160MHz 160MIPS 144-Pin LQFP 制造商:Analog Devices 功能描述:IC MICROCOMPUTER 16-BIT |

| adsp-2196mbca-140 | 制造商:Analog Devices 功能描述: |

| adsp-2196mbst-140 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 140MHz 140MIPS 144-Pin LQFP 制造商:Rochester Electronics LLC 功能描述: |

| ADSP-2196MBST-140Z | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 140MHz 140MIPS 144-Pin LQFP |

| ADSP-2196MKST-160 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 160MHz 160MIPS 144-Pin LQFP 制造商:Analog Devices 功能描述:16-Bit DSP 160 MIPs 2.5V 40 Kbytes |

發(fā)布緊急采購,3分鐘左右您將得到回復。