- 您現在的位置:買賣IC網 > PDF目錄374037 > ADSP-21MOD870-000 (ANALOG DEVICES INC) Internet Gateway Processor PDF資料下載

參數資料

| 型號: | ADSP-21MOD870-000 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 調制器/解調器 |

| 英文描述: | Internet Gateway Processor |

| 中文描述: | 56 kbps DATA, MODEM, PQFP100 |

| 封裝: | METRIC, PLASTIC, TQFP-100 |

| 文件頁數: | 11/32頁 |

| 文件大小: | 231K |

| 代理商: | ADSP-21MOD870-000 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

ADSP-21mod870

–11–

REV. 0

Unused bits in the 8-bit data memory formats are filled with 0s.

The BIAD register field is used to specify the starting address

for the on-chip memory involved with the transfer. The 14-bit

BEAD register specifies the starting address for the external byte

memory space. The 8-bit BMPAGE register specifies the start-

ing page for the external byte memory space. The BDIR register

field selects the direction of the transfer. Finally the, 14-bit

BWCOUNT register specifies the number of DSP words to

transfer and initiates the BDMA circuit transfers.

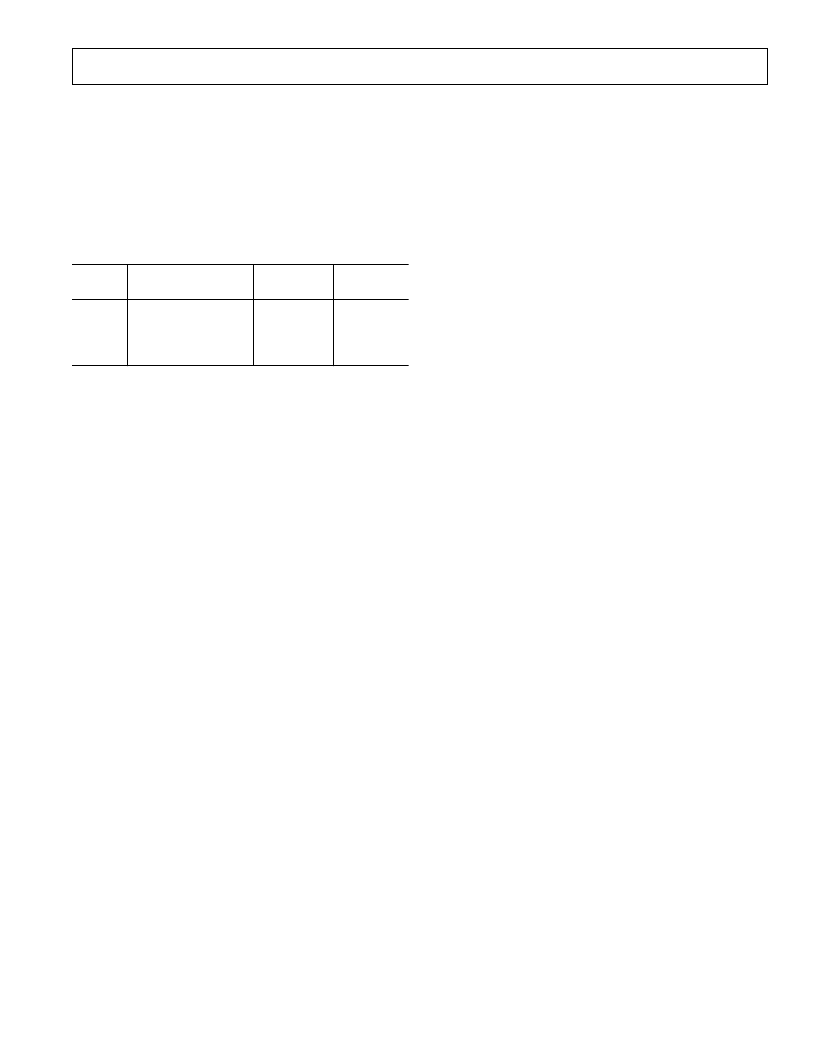

Table VI. Data Formats

Internal

Memory Space

BTYPE

Word Size

Alignment

00

01

10

11

Program Memory

Data Memory

Data Memory

Data Memory

24

16

8

8

Full Word

Full Word

MSBs

LSBs

BDMA accesses can cross page boundaries during sequential

addressing. A BDMA interrupt is generated on the completion

of the number of transfers specified by the BWCOUNT register.

The BWCOUNT register is updated after each transfer so it can

be used to check the status of the transfers. When it reaches zero,

the transfers have finished and a BDMA interrupt is generated.

The BMPAGE and BEAD registers must not be accessed by the

processor during BDMA operations.

The source or destination of a BDMA transfer will always be

on-chip program or data memory.

When the BWCOUNT register is written with a nonzero value,

the BDMA circuit starts executing byte memory accesses with

wait states set by BMWAIT. These accesses continue until the

count reaches zero. When enough accesses have occurred to

create a destination word, it is transferred to or from on-chip

memory. The transfer takes one processor cycle. Processor

accesses to external memory have priority over BDMA byte

memory accesses.

The BDMA Context Reset bit (BCR) controls whether the

processor is held off while the BDMA accesses are occurring.

Setting the BCR bit to 0 allows the processor to continue opera-

tions. Setting the BCR bit to 1 causes the processor to stop

execution while the BDMA accesses are occurring, to clear the

context of the processor, and start execution at address 0 when

the BDMA accesses have completed. The BDMA overlay bits

specify the OVLAY memory blocks to be accessed for internal

memory.

Internal Memory DMA Port (IDMA Port; Host Memory

Mode)

The IDMA Port provides an efficient means of communication

between a host system and the ADSP-21mod870. The port is

used to access the on-chip program memory and data memory

of the processor with only one processor cycle per word over-

head. The IDMA port cannot be used, however, to write to the

processor’s memory-mapped control registers. A typical IDMA

transfer process is described as follows:

1. Host starts IDMA transfer.

2. Host checks

IACK

control line to see if the processor is busy.

3

.

Host uses

IS

and IAL control lines to latch either the DMA

starting address (IDMAA) or the PM/DM OVLAY selection

into the processor’s IDMA control registers.

If IAD[15] = 1, the value of IAD[7:0] represents the IDMA

overlay: Bits 14:8 must be set to 0.

If IAD[15] = 0, the value of IAD[13:0] represents the start-

ing address of internal memory to be accessed and IAD[14]

reflects PM or DM for access.

4

.

Host uses

IS

and

IRD

(or

IWR

) to read (or write) processor

internal memory (PM or DM).

5

.

Host checks

IACK

line to see if the processor has completed

the previous IDMA operation.

6. Host ends IDMA transfer.

The IDMA port has a 16-bit multiplexed address and data bus

and supports 24-bit program memory. The IDMA port is com-

pletely asynchronous and can be written to while the ADSP-

21mod870 is operating at full speed.

The processor memory address is latched and is then automati-

cally incremented after each IDMA transaction. An external

device can therefore access a block of sequentially addressed

memory by specifying only the starting address of the block.

This increases throughput as the address does not have to be

sent for each memory access.

IDMA Port access occurs in two phases. The first is the IDMA

Address Latch cycle. When the acknowledge is asserted, a 14-bit

address and 1-bit destination type can be driven onto the bus by

an external device. The address specifies an on-chip memory

location; the destination type specifies whether it is a DM or

PM access. The falling edge of the address latch signal latches

this value into the IDMAA register.

Once the address is stored, data can then be either read from, or

written to, the ADSP-21mod870’s on-chip memory. Asserting

the select line (

IS

) and the appropriate read or write line (

IRD

and

IWR

respectively) signals the ADSP-21mod870 that a par-

ticular transaction is required. In either case, there is a one-

processor-cycle delay for synchronization. The memory access

consumes one additional processor cycle.

Once an access has occurred, the latched address is automati-

cally incremented, and another access can occur.

Through the IDMAA register, the processor can also specify the

starting address and data format for DMA operation. Asserting

the IDMA port select (

IS

) and address latch enable (IAL)

directs the ADSP-21mod870 to write the address onto the

IAD[14:0] bus into the IDMA Control Register. If IAD[15]

is set to 0, IDMA latches the address. If IAD[15] is set to 1,

IDMA latches OVLAY memory. This register, shown below, is

memory mapped at address DM (0x3FE0). Note that the latched

address (IDMAA) cannot be read back by the host.

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21XX1111 | ADSP-2100 Family DSP Microcomputers |

| ADSP-21XX4444 | ADSP-2100 Family DSP Microcomputers |

| ADSP-21MSP5859 | LM101A/LM201A/LM301A Operational Amplifiers; Package: MDIP; No of Pins: 8; Qty per Container: 40; Container: Rail |

| ADSP-21XX | ADSP-2100 Family DSP Microcomputers |

| ADSP-21MOD970-110 | Multiport Internet Gateway Processor Solution |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-21MOD880-000 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADSP-21MOD880NB000 | 制造商:Analog Devices 功能描述: |

| ADSP-21MOD885-000 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADSP-21MOD970-000 | 制造商:Analog Devices 功能描述: |

| ADSP-21MOD980-000 | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。