- 您現在的位置:買賣IC網 > PDF目錄374042 > ADUM1310 (Analog Devices, Inc.) Triple-Channel Digital Isolators PDF資料下載

參數資料

| 型號: | ADUM1310 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Triple-Channel Digital Isolators |

| 中文描述: | 三通道數字隔離器 |

| 文件頁數: | 5/20頁 |

| 文件大小: | 282K |

| 代理商: | ADUM1310 |

ADuM1310/ADuM1311

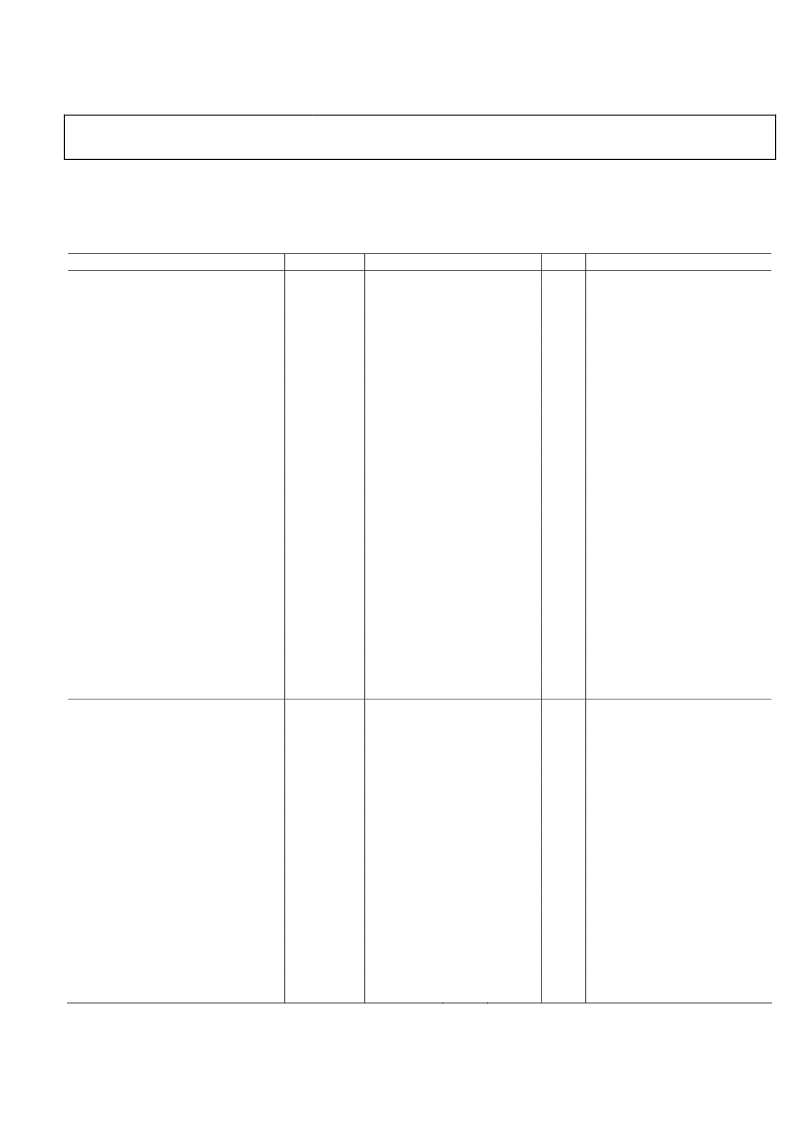

ELECTRICAL CHARACTERISTICS—3 V OPERATION

1

2.7 V ≤ V

DD1

≤ 3.6 V, 2.7 V ≤ V

DD2

≤ 3.6 V; all min/max specifications apply over the entire recommended operation range, unless

otherwise noted; all typical specifications are at T

A

= 25°C, V

DD1

= V

DD2

= 3.0 V.

Rev. F | Page 5 of 20

Table 2.

Parameter

DC SPECIFICATIONS

ADuM1310, Total Supply Current,

Three Channels

2

DC to 2 Mbps

V

DD1

Supply Current

V

DD2

Supply Current

10 Mbps (BRW Grade Only)

V

DD1

Supply Current

V

DD2

Supply Current

ADuM1311, Total Supply Current,

Three Channels

2

DC to 2 Mbps

V

DD1

Supply Current

V

DD2

Supply Current

10 Mbps (BRW Grade Only)

V

DD1

Supply Current

V

DD2

Supply Current

For All Models

Input Currents

Symbol

Min

Typ

Max

Unit

Test Conditions

I

DD1 (Q)

I

DD2 (Q)

I

DD1 (10)

I

DD2 (10)

1.2

0.8

3.4

1.1

1.6

1.0

4.9

1.3

mA

mA

mA

mA

DC to 1 MHz logic signal frequency

DC to 1 MHz logic signal frequency

5 MHz logic signal frequency

5 MHz logic signal frequency

I

DD1 (Q)

I

DD2 (Q)

I

DD1 (10)

I

DD2 (10)

I

IA

, I

IB

, I

IC

, I

CTRL1

,

I

CTRL2

, I

DISABLE

10

1.0

0.9

2.5

1.9

+0.01

1.6

1.4

3.5

2.6

+10

mA

mA

μA

DC to 1 MHz logic signal frequency

DC to 1 MHz logic signal frequency

5 MHz logic signal frequency

5 MHz logic signal frequency

0 ≤ V

IA

, V

IB

, V

IC

≤ V

DD1

or V

DD2

,

0 ≤ V

CTRL1

, V

CTRL2

≤ V

DD1

or V

DD2

,

0 ≤ V

DISABLE

≤ V

DD1

I

Ox

= 20 μA, V

Ix

= V

IxH

I

Ox

= 4 mA, V

Ix

= V

IxH

I

Ox

= 20 μA, V

Ix

= V

IxL

I

Ox

= 4 mA, V

Ix

= V

IxL

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

Logic High Input Threshold

Logic Low Input Threshold

Logic High Output Voltages

V

IH

V

IL

V

OAH

, V

OBH

, V

OCH

1.6

V

DD1

, V

DD2

0.1 3.0

V

DD1

, V

DD2

0.4 2.8

1

20

10

20

0.4

0.1

0.4

1000

100

40

50

50

100

50

5

30

5

V

V

V

V

V

V

ns

Mbps

ns

ns

ns

ns

ns

Mbps

ns

ns

ps/°C

ns

ns

0.0

0.2

30

5

Logic Low Output Voltages

V

OAL

, V

OBL

, V

OCL

SWITCHING SPECIFICATIONS

ADuM131xARW

Minimum Pulse Width

3

Maximum Data Rate

4

Propagation Delay

5

Pulse Width Distortion, |t

PLH

t

PHL

|

5

Propagation Delay Skew

6

Channel-to-Channel Matching

7

ADuM131xBRW

Minimum Pulse Width

3

Maximum Data Rate

4

Propagation Delay

5

Pulse Width Distortion, |t

PLH

t

PHL

|

5

Change vs. Temperature

Propagation Delay Skew

6

Channel-to-Channel Matching,

Codirectional Channels

7

Channel-to-Channel Matching,

Opposing-Directional Channels

7

PW

t

PHL

, t

PLH

PWD

t

PSK

t

PSKCD/OD

PW

t

PHL

, t

PLH

PWD

t

PSK

t

PSKCD

t

PSKOD

6

ns

C

L

= 15 pF, CMOS signal levels

相關PDF資料 |

PDF描述 |

|---|---|

| ADUM1310_07 | Triple-Channel Digital Isolators |

| ADuM1310ARWZ1 | Triple-Channel Digital Isolators |

| ADuM1310BRWZ1 | Triple-Channel Digital Isolators |

| ADuM1310BRWZ-RL1 | Triple-Channel Digital Isolators |

| ADUM1311 | Triple-Channel Digital Isolators |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADUM1310_07 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Triple-Channel Digital Isolators |

| ADUM1310_08 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Triple-Channel Digital Isolators |

| ADUM1310ARWZ | 功能描述:IC ISOLATOR DGTL 3CHAN 16-SOIC RoHS:是 類別:隔離器 >> 數字隔離器 系列:iCoupler® 標準包裝:66 系列:iCoupler® 輸入 - 1 側/2 側:2/2 通道數:4 電源電壓:3.3V,5V 電壓 - 隔離:2500Vrms 數據速率:25Mbps 傳輸延遲:60ns 輸出類型:邏輯 封裝/外殼:20-SSOP(0.209",5.30mm 寬) 供應商設備封裝:20-SSOP 包裝:管件 工作溫度:-40°C ~ 105°C |

| ADUM1310ARWZ1 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Triple-Channel Digital Isolators |

| ADUM1310ARWZ-RL | 功能描述:IC ISOLATOR DGTL 3CH 16SOIC RoHS:是 類別:隔離器 >> 數字隔離器 系列:iCoupler® 標準包裝:66 系列:iCoupler® 輸入 - 1 側/2 側:2/2 通道數:4 電源電壓:3.3V,5V 電壓 - 隔離:2500Vrms 數據速率:25Mbps 傳輸延遲:60ns 輸出類型:邏輯 封裝/外殼:20-SSOP(0.209",5.30mm 寬) 供應商設備封裝:20-SSOP 包裝:管件 工作溫度:-40°C ~ 105°C |

發布緊急采購,3分鐘左右您將得到回復。