- 您現在的位置:買賣IC網 > PDF目錄374044 > ADUM5240BRZ (ANALOG DEVICES INC) Dual-Channel Isolators with Integrated DC/DC Converter, 50 mW PDF資料下載

參數資料

| 型號: | ADUM5240BRZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 模擬信號調理 |

| 英文描述: | Dual-Channel Isolators with Integrated DC/DC Converter, 50 mW |

| 中文描述: | SPECIALTY ANALOG CIRCUIT, PDSO8 |

| 封裝: | LEAD FREE, MS-012AA, SOIC-8 |

| 文件頁數: | 3/10頁 |

| 文件大小: | 152K |

| 代理商: | ADUM5240BRZ |

Preliminary Technical Data

ADuM5240/ADuM5241/ADuM5242

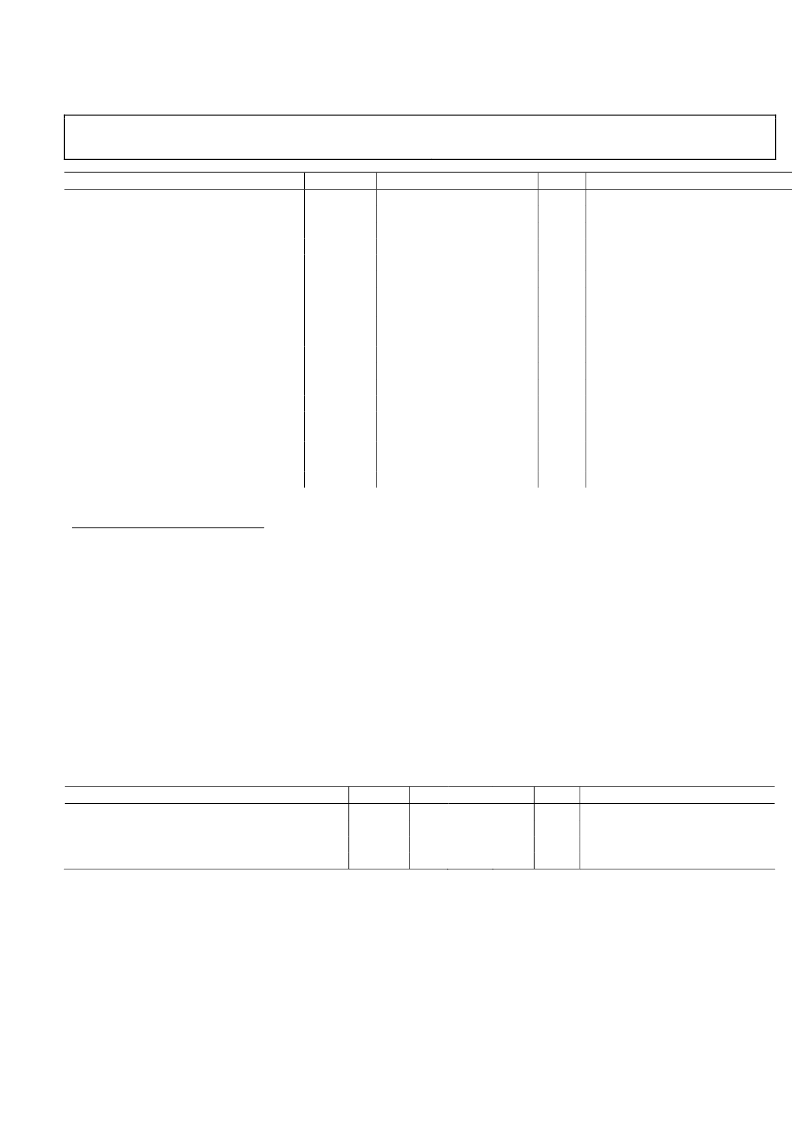

Parameter

AC SPECIFICATIONS

Minimum Pulse Width

5

Maximum Data Rate

6

Propagation Delay

7

Pulse-Width Distortion, |t

PLH

t

PHL

|

7

Propagation Delay Skew

8

Channel-to-Channel Matching,

Codirectional Channels

9

Channel-to-Channel Matching,

Opposing-Directional Channels

10

Ripple

11

Enable Time

12

Disable Time

12

Output Rise/Fall Time (10% to 90%)

Common-Mode Transient Immunity

at Logic High Output

Common-Mode Transient Immunity

at Logic Low Output

Refresh Frequency

Rev. PrN | Page 3 of 10

Symbol

PW

t

PHL

, t

PLH

PWD

t

PSK

t

PSKCD

Min

10

25

Typ

Max

100

70

3

45

3

Unit

ns

Mbps

ns

ns

ns

ns

Test Conditions

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

C

L

= 15 pF, CMOS signal levels

t

PSKCD

15

ns

C

L

= 15 pF, CMOS signal levels

T

ENABLE

T

DISABLE

t

R

/t

F

|CM

H

|

25

200

50

50

2.5

35

mV

P-P

ns

ns

ns

kV/μs

C

L

= 15 pF, CMOS signal levels

V

Ix

= V

DD

, V

ISO

, V

CM

= 1000 V,

transient magnitude = 800 V

V

Ix

= 0 V, V = 1000 V,

transient magnitude = 800 V

|CM

L

|

25

35

kV/μs

f

r

1.0

MHz

1

All voltages are relative to their respective ground.

2

Supply current values are specified with no load present on the digital outputs.

3

Supply current values are specified with no load present on the digital outputs.

4

Enable/disable threshold is the voltage at which the internal DC/DC converter is enabled/disabled.

5

The minimum pulse width is the shortest pulse width at which the specified pulse-width distortion is guaranteed.

6

The maximum data rate is the fastest data rate at which the specified pulse-width distortion is guaranteed.

7

t

PHL

propagation delay is measured from the 50% level of the falling edge of the V

Ix

signal to the 50% level of the falling edge of the V

Ox

signal. t

PLH

propagation delay is

measured from the 50% level of the rising edge of the V

Ix

signal to the 50% level of the rising edge of the V

Ox

signal.

8

t

PSK

is the magnitude of the worst-case difference in t

PHL

and/or t

PLH

that is measured between units at the same operating temperature, supply voltages, and output

load within the recommended operating conditions.

9

Channel-to-channel matching is the absolute value of the difference in propagation delays between the two channels when operated with identical loads.

10

Channel-to-channel matching is the absolute value of the difference in propagation delays between the two channels when operated with identical loads.

11

Ripple occurs at frequency corresponding to the input signal data rate or the refresh frequency for data rates below 1Mbps.

12

Enable time is the duration from when input supply voltage rises above the enable threshold to when the internal DC/DC converter starts charging an external load.

Disable time is the duration from when the input supply voltage drops below the disable threshold to when the internal DC/DC converter stops charging an external

load

PACKAGE CHARACTERISTICS

Table 2.

Parameter

Resistance (Input-Output)

Capacitance (Input-Output)

Input Capacitance

IC Junction-to-Air Thermal Resistance

Symbol

R

I-O

C

I-O

C

I

θ

JA

Min

Typ

10

12

1.0

4.0

150

Max

Unit

Ω

pF

pF

°C/W

Test Conditions

f = 1 MHz

相關PDF資料 |

PDF描述 |

|---|---|

| ADUM5241 | Dual-Channel Isolators with Integrated DC/DC Converter, 50 mW |

| ADUM5241BRZ | Dual-Channel Isolators with Integrated DC/DC Converter, 50 mW |

| ADUM5242 | Dual-Channel Isolators with Integrated DC/DC Converter, 50 mW |

| ADUM5242BRZ | Dual-Channel Isolators with Integrated DC/DC Converter, 50 mW |

| ADUuC7027BSTZ62-RL | Precision Analog Microcontroller 12-bit Analog I/O, ARM7TDMI MCU |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADUM5240XRZ | 制造商:Analog Devices 功能描述:DUAL-CHANNEL ISOLATORS WITH INTEGRATED DC/DC CONVERTER - Rail/Tube |

| ADUM5241 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Dual-Channel Isolators with Integrated DC/DC Converter, 50 mW |

| ADUM5241ARZ | 功能描述:IC ISOLATOR 2CH W/CONV 8-SOIC RoHS:是 類別:隔離器 >> 數字隔離器 系列:IsoPower®, iCoupler® 標準包裝:66 系列:iCoupler® 輸入 - 1 側/2 側:2/2 通道數:4 電源電壓:3.3V,5V 電壓 - 隔離:2500Vrms 數據速率:25Mbps 傳輸延遲:60ns 輸出類型:邏輯 封裝/外殼:20-SSOP(0.209",5.30mm 寬) 供應商設備封裝:20-SSOP 包裝:管件 工作溫度:-40°C ~ 105°C |

| ADUM5241ARZ-RL7 | 功能描述:IC ISOLATOR 2CH W/CONV 8-SOIC RoHS:是 類別:隔離器 >> 數字隔離器 系列:IsoPower®, iCoupler® 標準包裝:66 系列:iCoupler® 輸入 - 1 側/2 側:2/2 通道數:4 電源電壓:3.3V,5V 電壓 - 隔離:2500Vrms 數據速率:25Mbps 傳輸延遲:60ns 輸出類型:邏輯 封裝/外殼:20-SSOP(0.209",5.30mm 寬) 供應商設備封裝:20-SSOP 包裝:管件 工作溫度:-40°C ~ 105°C |

| ADUM5241BRZ | 制造商:Analog Devices 功能描述:DGTL ISOLATORS 8SOIC - Rail/Tube |

發布緊急采購,3分鐘左右您將得到回復。