- 您現在的位置:買賣IC網 > PDF目錄374045 > ADV7122KP30 (ANALOG DEVICES INC) CMOS 80 MHz, Triple 10-Bit Video DACs PDF資料下載

參數資料

| 型號: | ADV7122KP30 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | DAC |

| 英文描述: | CMOS 80 MHz, Triple 10-Bit Video DACs |

| 中文描述: | TRIPLE, PARALLEL, 8 BITS INPUT LOADING, 10-BIT DAC, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數: | 6/12頁 |

| 文件大小: | 196K |

| 代理商: | ADV7122KP30 |

ADV7121/ADV7122

–6–

REV. B

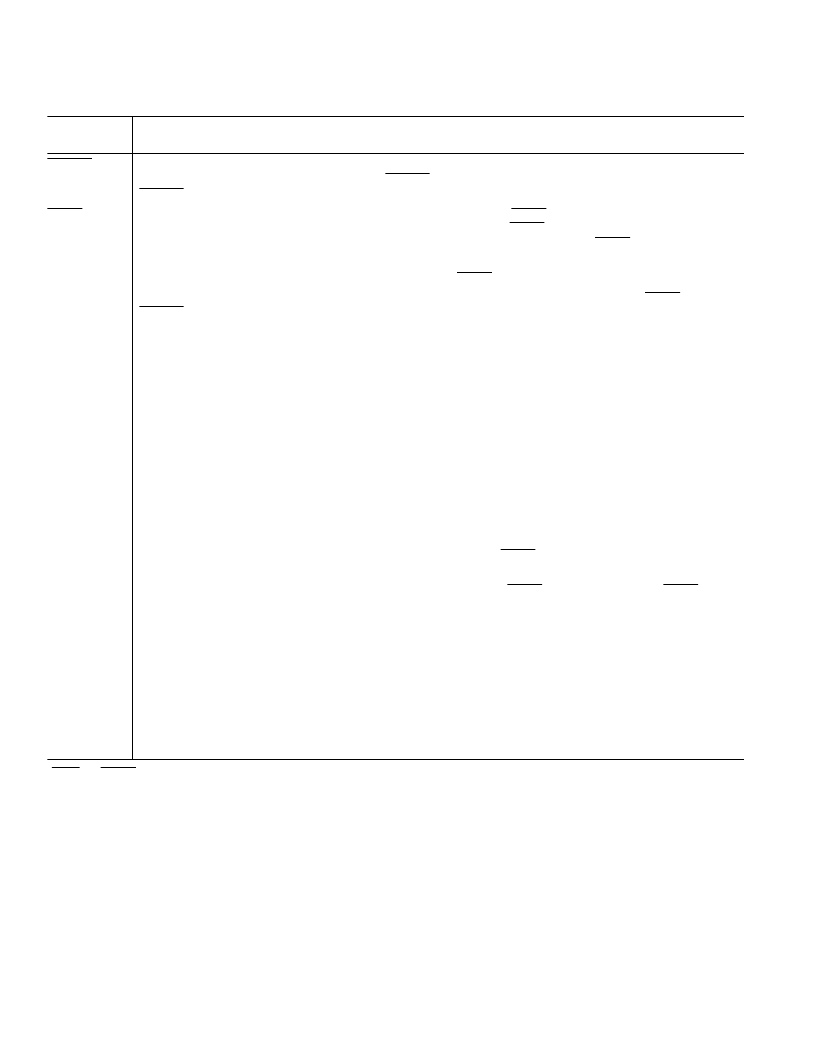

PIN FUNCT ION DE SCRIPT ION

Pin

Mnemonic

Function

BLANK

*

Composite blank control input (T T L compatible). A logic zero on this control input drives the analog outputs,

IOR, IOB and IOG, to the blanking level. T he

BLANK

signal is latched on the rising edge of CLOCK . While

BLANK

is a logical zero, the R0–R9, G0–G9 and R0–R9 pixel inputs are ignored.

Composite sync control input (T T L compatible). A logical zero on the

SYNC

input switches off a 40 IRE

current source. T his is internally connected to the IOG analog output.

SYNC

does not override any other

control or data input, therefore, it should only be asserted during the blanking interval.

SYNC

is latched on the

rising edge of CLOCK .

If sync information is not required on the green channel, the

SYNC

input should be tied to logical zero.

Clock input (T T L compatible). T he rising edge of CLOCK latches the R0–R9, G0–G9, B0–B9,

SYNC

and

BLANK

pixel and control inputs. It is typically the pixel clock rate of the video system. CLOCK should be

driven by a dedicated T T L buffer.

Red, green and blue pixel data inputs (T T L compatible). Pixel data is latched on the rising edge of CLOCK .

R0, G0 and B0 are the least significant data bits. Unused pixel data inputs should be connected to either the

regular PCB power or ground plane.

IOR, IOG, IOB Red, green, and blue current outputs. T hese high impedance current sources are capable of directly driving a

doubly terminated 75

coaxial cable. All three current outputs should have similar output loads whether or not

they are all being used.

FS ADJUST

Full-scale adjust control. A resistor (R

SET

) connected between this pin and GND, controls the magnitude of the

full-scale video signal. Note that the IRE relationships are maintained, regardless of the full-scale output current.

T he relationship between R

SET

and the full-scale output current on IOG (assuming I

SYNC

is connected to IOG)

is given by:

R

SET

(

)

= 12,082

×

V

REF

(V)/IOG (mA)

T he relationship between R

SET

and the full-scale output current on IOR, IOG and IOB is given by:

IOG* (mA)

= 12,082

×

V

REF

(V)/R

SET

(

) (

SYNC

being asserted)

IOR, IOB (mA)

= 8,628

×

V

REF

(V)/R

SET

(

)

T he equation for IOG will be the same as that for IOR and IOB when

SYNC

is not being used, i.e.,

SYNC

tied permanently low. For the ADV7121, all three analog output currents are as described by:

IOR, IOG, IOB (mA)

= 7,969

×

V

REF

(V)/R

SET

(

)

COMP

Compensation pin. T his is a compensation pin for the internal reference amplifier. A 0.1

μ

F ceramic capacitor

must be connected between COMP and V

AA

.

V

REF

Voltage reference input. An external 1.23 V voltage reference must be connected to this pin. T he use of an

external resistor divider network is not recommended. A 0.1

μ

F decoupling ceramic capacitor should be

connected between V

REF

and V

AA

.

V

AA

Analog power supply (5 V

±

5%). All V

AA

pins on the ADV7121/ADV7122 must be connected.

GND

Ground. All GND pins must be connected.

SYNC

*

CLOCK

R0–R9,

G0–G9,

B0–B9

*

SYNC

and

BLANK

functions are not provided on the ADV7121.

相關PDF資料 |

PDF描述 |

|---|---|

| ADV7122KP50 | CMOS 80 MHz, Triple 10-Bit Video DACs |

| ADV7122KP80 | CMOS 80 MHz, Triple 10-Bit Video DACs |

| ADV7121KN30 | CMOS 80 MHz, Triple 10-Bit Video DACs |

| ADV7122 | 80 MHz, Triple 10-Bit Video DACs(80MHz,三通道10位視頻D/A轉換器) |

| ADV7123KST140 | CMOS, 240 MHz Triple 10-Bit High Speed Video DAC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV7122KP50 | 制造商:Rochester Electronics LLC 功能描述:TRIPLE 10 BIT VIDEO DAC - Bulk 制造商:Analog Devices 功能描述: |

| ADV7122KP50-REEL | 制造商:Analog Devices 功能描述:DAC 3-CH Segment 10-bit 44-Pin PLCC T/R 制造商:Rochester Electronics LLC 功能描述:TRIPLE 10 BIT VIDEO DAC - Tape and Reel |

| ADV7122KP80 | 制造商:Rochester Electronics LLC 功能描述:TRIPLE 10 BIT VIDEO DAC - Bulk 制造商:Analog Devices 功能描述: |

| ADV7122KPZ30 | 制造商:Analog Devices 功能描述:DAC 3-CH Segment 10-bit 44-Pin PLCC |

| ADV7122KPZ80 | 制造商:Analog Devices 功能描述:DAC 3-CH Segment 10-bit 44-Pin PLCC |

發布緊急采購,3分鐘左右您將得到回復。