- 您現在的位置:買賣IC網 > PDF目錄374046 > ADV7173* (Analog Devices, Inc.) Digital PAL/NTSC Video Encoder with Six DACs (10 Bits). Color Control and Enhanced Power Management PDF資料下載

參數資料

| 型號: | ADV7173* |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Digital PAL/NTSC Video Encoder with Six DACs (10 Bits). Color Control and Enhanced Power Management |

| 中文描述: | 數碼PAL / NTSC視頻編碼器與六數模轉換器(10位)。色彩控制和增強的電源管理 |

| 文件頁數: | 46/59頁 |

| 文件大小: | 455K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

ADV7172/ADV7173

–46–

REV. A

APPENDIX 5

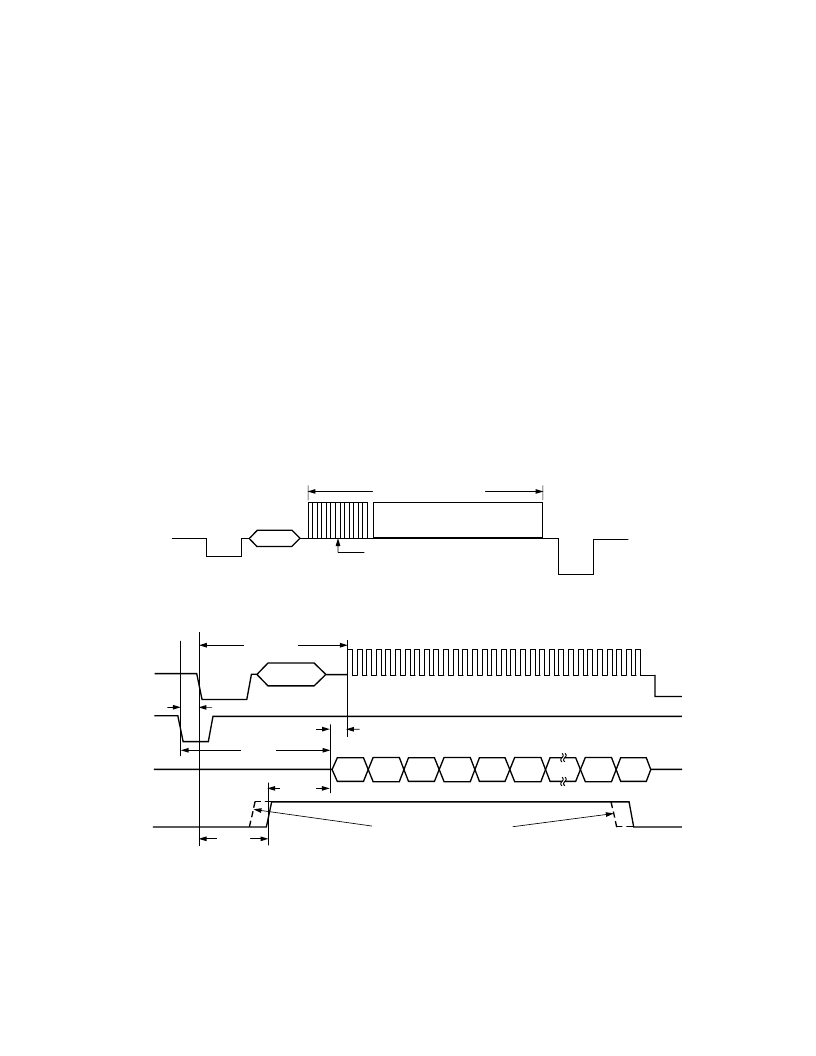

TELETEXT INSERTION

Time, t

PD,

is the time needed by the ADV7172/ADV7173 to interpolate input data on TTX and insert it onto the CVBS or Y out-

puts, such that it appears t

SYNTXTOUT

= 10.2

μ

s after the leading edge of the horizontal signal. Time, TXT

DEL

, is the pipeline delay

time by the source that is gated by the TTREQ signal in order to deliver TTX data.

With the programmability offered with TTXREQ signal on the Rising/Falling edges, the TTX data is always inserted at the correct

position of 10.2

μ

s after the leading edge of horizontal sync pulse, thus enabling a source interface with variable pipeline delays.

The width of the TTXREQ signal must always be maintained such that it allows the insertion of 360 (in order to comply with the

Teletext Standard “PAL-WST”) teletext bits at a text data rate of 6.9375 Mbits/s. This is achieved by setting TC03–TC00 to “0.”

The insertion window is not open if the Teletex Enable bit (MR34) is set to “0.”

Teletext Protocol

The relationship between the TTX bit clock (6.9375 MHz) and the system CLOCK (27 MHz) for 50 Hz is given as follows:

(27 MHz/4) = 6.75 MHz

(6.9375

×

10

6

/6.75

×

10

6

) = 1.027777

Thus 37 TTX bits correspond to 144 clocks (27 MHz) and each bit has a width of almost four clock cycles. The ADV7172/ADV7173

uses an internal sequencer and variable phase interpolation filter to minimize the phase jitter and thus generate a bandlimited signal

that can be outputted on the CVBS and Y outputs.

At the TTX input the bit duration scheme repeats after every 37 TTX bits or 144 clock cycles. The protocol requires that TTX Bits

10, 19, 28, 37 are carried by three clock cycles, all other bits by four clock cycles. After 37 TTX bits, the next bits with three clock

cycles are 47, 56, 65 and 74. This scheme holds for all following cycles of 37 TTX bits, until all 360 TTX bits are completed. All

teletext lines are implemented in the same way. Individual control of teletext lines is controlled by Teletext Setup Registers.

ADDRESS & DATA

RUN-IN CLOCK

TELETEXT VBI LINE

45 BYTES (360 BITS) – PAL

Figure 72. Teletext VBI Line

PROGRAMMABLE PULSE EDGES

t

PD

t

PD

CVBS/Y

HSYNC

TXTREQ

TXT

DATA

t

SYNTXTOUT

= 10.2

m

s

t

TXT

DEL

= TTXREQ TO TTX (PROGRAMMABLE RANGE = 4 BITS [0–15 CLOCK CYCLES])

t

SYNTXTOUT

10.2

m

s

TXT

DEL

TXT

ST

Figure 73. Teletext Functionality Diagram

相關PDF資料 |

PDF描述 |

|---|---|

| ADV7174 | Chip Scale PAL/NTSC Video Encoder with Advanced Power Management |

| ADV7174BCP | Chip Scale PAL/NTSC Video Encoder with Advanced Power Management |

| ADV7174BCP-REEL | Chip Scale PAL/NTSC Video Encoder with Advanced Power Management |

| ADV7174KCP | Chip Scale PAL/NTSC Video Encoder with Advanced Power Management |

| ADV7174KCP-REEL | Chip Scale PAL/NTSC Video Encoder with Advanced Power Management |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV7173KST | 制造商:Rochester Electronics LLC 功能描述:6-DAC NTSC/PAL ENCODER I.C. - Tape and Reel 制造商:Analog Devices 功能描述:IC VIDEO ENCODER |

| ADV7173KST-REEL | 制造商:Analog Devices 功能描述:Video Encoder 6DAC 10-Bit 48-Pin LQFP T/R |

| ADV7173KSTZ | 功能描述:IC DAC VIDEO NTSC 6-CH 48LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編碼器,解碼器,轉換器 系列:- 產品變化通告:Development Systems Discontinuation 26/Apr/2011 標準包裝:1 系列:- 類型:編碼器 應用:DVB-S.2 系統 電壓 - 電源,模擬:- 電壓 - 電源,數字:- 安裝類型:- 封裝/外殼:模塊 供應商設備封裝:模塊 包裝:散裝 其它名稱:Q4645799 |

| ADV7173KSTZ-REEL | 功能描述:IC DAC VIDEO NTSC 6-CH 48LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編碼器,解碼器,轉換器 系列:- 產品變化通告:Development Systems Discontinuation 26/Apr/2011 標準包裝:1 系列:- 類型:編碼器 應用:DVB-S.2 系統 電壓 - 電源,模擬:- 電壓 - 電源,數字:- 安裝類型:- 封裝/外殼:模塊 供應商設備封裝:模塊 包裝:散裝 其它名稱:Q4645799 |

發布緊急采購,3分鐘左右您將得到回復。