- 您現在的位置:買賣IC網 > PDF目錄374046 > ADV7175A (Analog Devices, Inc.) High Quality, 10-Bit, Digital CCIR-601 to PAL/NTSC Video Encoder PDF資料下載

參數資料

| 型號: | ADV7175A |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | High Quality, 10-Bit, Digital CCIR-601 to PAL/NTSC Video Encoder |

| 中文描述: | 高品質,10位,數字無線電咨詢委員會,601到PAL / NTSC制式視頻編碼器 |

| 文件頁數: | 31/52頁 |

| 文件大小: | 629K |

| 代理商: | ADV7175A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADV7175A/ADV7176A

–31–

REV. B

APPE NDIX 3

T E LE T E X T INSE RT ION

T ime T

PD

time needed by the ADV7175A/ADV7176A to interpolate input data on T T X and insert it onto the CVBS or Y outputs,

such that it appears T

synT xtOut

= 10.2

μ

s after the leading edge of the horizontal signal. T ime T xt

Del

is the pipeline delay time by the

source that is gated by the T T REQ signal in order to deliver T T X data.

With the programmability that is offered with T T X REQ signal on the Rising/Falling edges, the T T X data is always inserted at the

correct position of 10.2

μ

s after the leading edge of Horizontal Sync pulse, which enables a source interface with variable pipeline

delays.

T he width of the T T X REQ signal must always be maintained so it allows the insertion of 360 (to comply with the T eletext Standard

“PAL–WST ”) teletext bits at a text data rate of 6.9375 Mbits/s; this is achieved by setting T C03–T C00 to zero. T he insertion win-

dow is not open if the T eletext Enable bit (MR34) is set to zero.

T eletext Protocol

T he relationship between the T T X bit clock (6.9375 MHz) and the system CLOCK (27 MHz) for 50 Hz is given as follows:

27

MHz

4

=

6.75

MHz

6.9375

×

10

6

6.75

×

10

6

=

1.027777

T hus 37 T T X bits correspond to 144 clocks (27 MHz) and each bit has a width of almost four clock cycles. T he ADV7175A/ADV7176A

uses an internal sequencer and variable phase interpolation filter to minimize the phase jitter and thus generate a bandlimited signal

which can be outputted on the CVBS and Y outputs.

At the T T X input the bit duration scheme repeats after every 37 T T X bits or 144 clock cycles. T he protocol requires that T T X bits

10, 19, 28, 37 are carried by three clock cycles, all other bits by four clock cycles. After 37 T T X bits, the next bits with three clock

cycles are 47, 56, 65 and 74. T his scheme holds for all following cycles of 37 T T X bits, until all 360 T T X bits are completed. All

teletext lines are implemented in the same way. Individual control of teletext lines are controlled by T eletext Setup Registers.

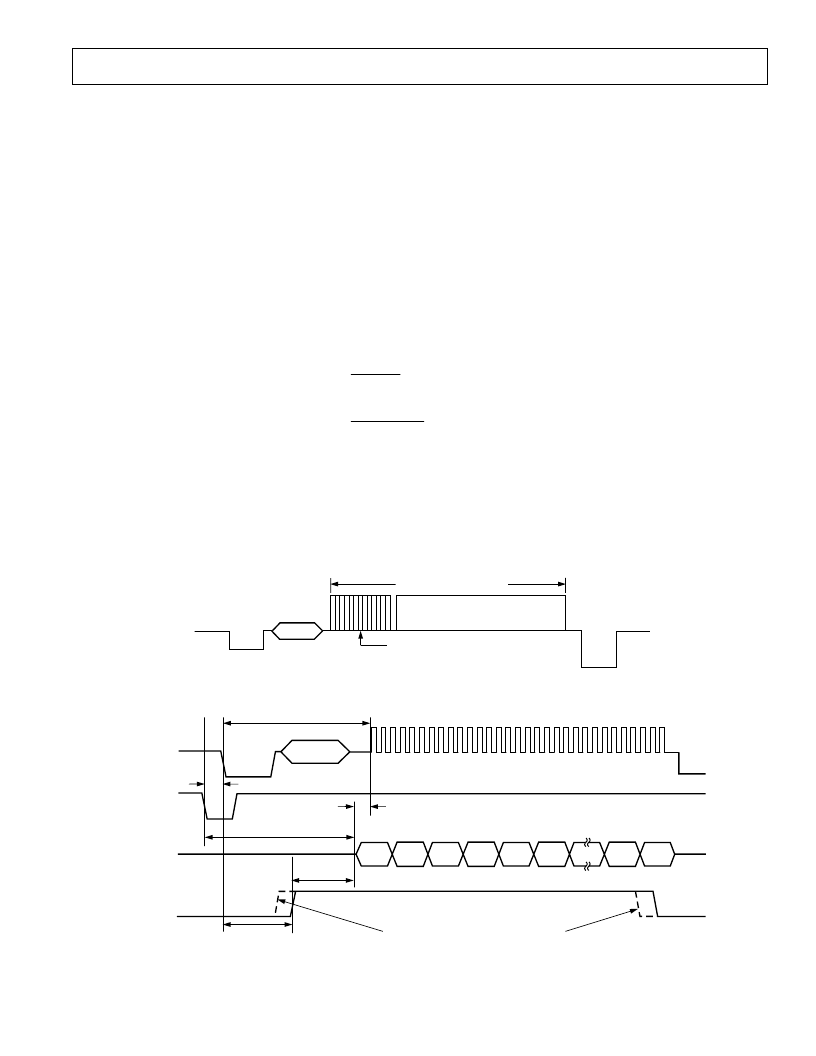

ADDRESS & DATA

RUN-IN CLOCK

TELETEXT VBI LINE

45 BYTES (360 BITS) – PAL

Figure 47. Teletext VBI Line

PROGRAMMABLE PULSE EDGES

t

SYNTXTOUT

t

PD

t

PD

10.2

m

s

TXT

ST

TXT

DEL

CVBS/Y

HSYNC

TXTREQ

TXT

DATA

t

SYNTXTOUT

= 10.2

m

s

t

= PIPELINE DELAY THROUGH ADV7175A/ADV7176A

TXT

DEL

= TTXREQ TO TTX (PROGRAMMABLE RANGE = 4 BITS [0–15 CLOCK CYCLES])

Figure 48. Teletext Functionality Diagram

相關PDF資料 |

PDF描述 |

|---|---|

| ADV7175AKS | High Quality, 10-Bit, Digital CCIR-601 to PAL/NTSC Video Encoder |

| ADV7176A | High Quality, 10-Bit, Digital CCIR-601 to PAL/NTSC Video Encoder |

| ADV7176AKS | High Quality, 10-Bit, Digital CCIR-601 to PAL/NTSC Video Encoder |

| ADV7176A* | High Quality. 10-Bit. Digital CCIR-601 to PAL/NTSC Video Encoder |

| ADV7175 | Integrated Digital CCIR-601 YCrCb to PAL/NTSC Video Encoder |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV7175AKS | 制造商:AD 制造商全稱:Analog Devices 功能描述:High Quality, 10-Bit, Digital CCIR-601 to PAL/NTSC Video Encoder |

| ADV7175KS | 制造商:AD 制造商全稱:Analog Devices 功能描述:Integrated Digital CCIR-601 YCrCb to PAL/NTSC Video Encoder |

| ADV7176 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Integrated Digital CCIR-601 YCrCb to PAL/NTSC Video Encoder |

| ADV7176A | 制造商:AD 制造商全稱:Analog Devices 功能描述:High Quality, 10-Bit, Digital CCIR-601 to PAL/NTSC Video Encoder |

發布緊急采購,3分鐘左右您將得到回復。