- 您現在的位置:買賣IC網 > PDF目錄374047 > ADV7192KST (ANALOG DEVICES INC) Video Encoder with Six 10-Bit DACs, 54 MHz Oversampling and Progressive Scan Inputs PDF資料下載

參數資料

| 型號: | ADV7192KST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 顏色信號轉換 |

| 英文描述: | Video Encoder with Six 10-Bit DACs, 54 MHz Oversampling and Progressive Scan Inputs |

| 中文描述: | COLOR SIGNAL ENCODER, PQFP80 |

| 封裝: | LQFP-80 |

| 文件頁數: | 35/69頁 |

| 文件大小: | 664K |

| 代理商: | ADV7192KST |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

ADV7192

–35–

REV. 0

CLAMP/

VSO

Select (MR77)

This bit is used to select the functionality of Pin 62. Setting this

bit to 1 selects CLAMP as the output signal. A 0 selects

VSO

as the output signal. Since this pin is also shared with the TTX

functionality, TTX Input/CLAMP–

VSO

Output has to be set

accordingly (MR76).

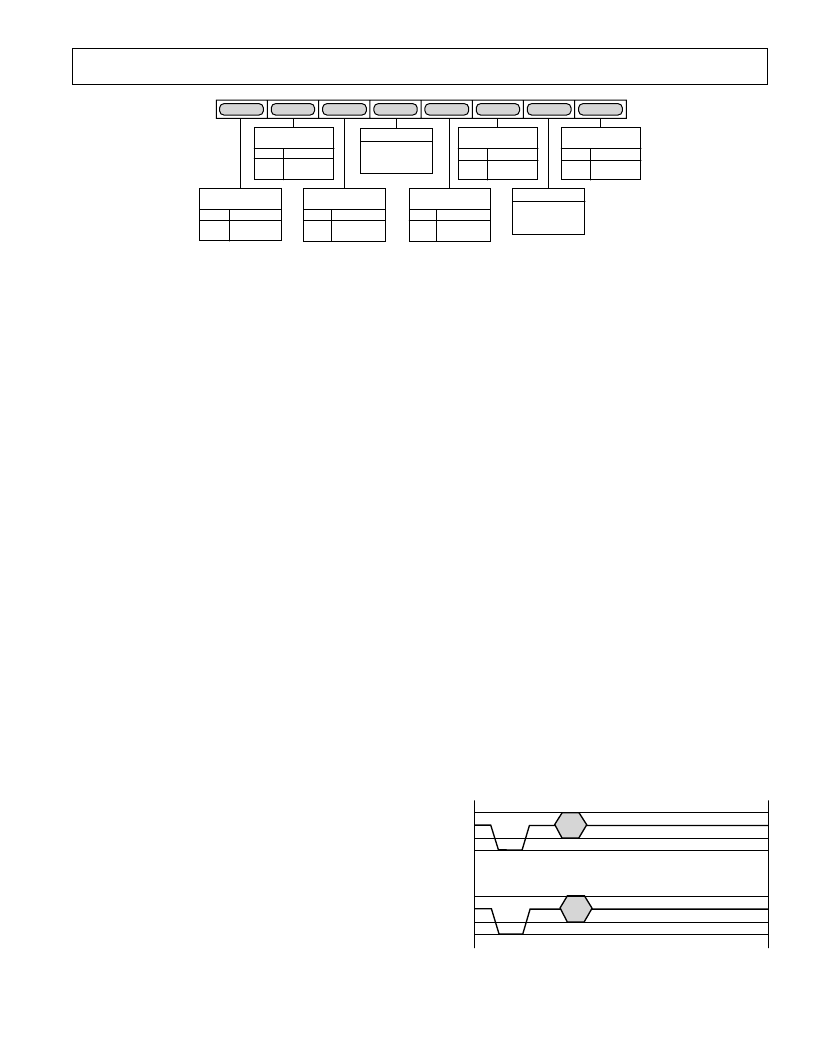

MODE REGISTER 8

MR8 (MR87–MR80)

(Address (SR4–SR0) = 08H)

Mode Register 8 is an 8-bit-wide register. Figure 64 shows the

various operations under the control of Mode Register 8.

MR8 BIT DESCRIPTION

Progressive Scan Control (MR80)

This control enables the progressive scan inputs on pins

Y(0)/P8–Y(7)/P15, Y(8)–Y(9), Cr(0)–Cr(9), Cb(0)–Cb(9)

.

To

enable this control MR80 has to be set to 1. It is assumed that

the incoming

Y

data contains all necessary sync information.

Note: Simultaneous progressive scan input and 16-bit pixel input

is not possible.

Reserved (MR81)

A 0 must be written to this bit.

Double Buffer Control (MR82)

Double Buffering can be enabled or disabled on the Contrast

Control Register, U Scale Register, V Scale Register, Hue Adjust

Control Register, Closed Captioning Register, Brightness Control

Register, Gamma Curve Select Bit and the Macrovision Regis-

ters. Double Buffer is not available in Master Mode.

16-Bit Pixel Port (MR83)

This bit controls if the ADV7192 is operated in 8-bit or 16-bit

mode. In 8-bit mode the input data will be set up on Pins P0–P7.

Reserved (MR84)

A Logic 0 must be written to this bit.

DNR Enable Control (MR85)

To enable the DNR process this bit has to be set to 1. If this bit

is set to other DNR processing is bypassed. For further informa-

tion on DNR controls see DNR Mode Control section.

Gamma Enable Control (MR86)

To enable the programmable gamma correction this bit has

to be set to enabled (MR86 = 1). For further information on

Gamma Correction controls see Gamma Correction Registers

section.

Gamma Curve Select Control (MR87)

This bit selects which of the two programmable gamma curves is

to be used. When setting MR87 to 0, the gamma correction curve

selected is Curve A. Otherwise, Curve B is selected. Each curve

will have to be programmed by the user. For further information

on Gamma Correction controls see Gamma Correction Regis-

ters section.

MODE REGISTER 9

MR9 (MR97–MR90)

(Address (SR4–SR0) = 09H)

Mode Register 9 is an 8-bit-wide register. Figure 66 shows the

various operations under the control of Mode Register 9.

MR9 BIT DESCRIPTION

Undershoot Limiter (MR90–MR91)

This control ensures that no luma video data will go below a

programmable level. This prevents any synchronization problems

due to luma signals going below the blanking level. Available

limit levels are –1.5 IRE, –6 IRE, –11 IRE. Note that this facility is

only available in 4

×

Oversampling mode (MR16 = 1). When the

device is operated in 2

×

Oversampling mode (MR16 = 0) or RGB

output without RGB sync are selected, the minimum luma level is

set in Timing Register 0, TR06 (Min Luma Control).

Black Burst Y DAC (MR92)

It is possible to output a Black Burst signal from the DAC

which is selected to be the Luma DAC (MR22, MR21, MR20).

This signal can be useful for locking two video sources together

using professional video equipment. See also Black Burst Out-

put section.

Black Burst Luma (MR93)

It is possible to output a Black Burst signal from the DAC which

is selected to be the Y-DAC (MR22, MR21, MR20). This signal

can be useful for locking two video sources together using pro-

fessional video equipment. See also Black Burst Output section.

20 IRE

0 IRE

–20 IRE

–40 IRE

21.5 IRE

0 IRE

–21.5 IRE

–43 IRE

3.58MHz

COLOR BURST

(9 CYCLES)

4.43MHz

COLOR BURST

(10 CYCLES)

NTSC BLACK BURST SIGNAL

PAL BLACK BURST SIGNAL

Figure 65. Black Burst Signals for PAL and NTSC Standards

ZERO SHOULD

BE WRITTEN

TO THIS BIT

MR84

MR87

MR86

MR85

MR84

MR83

MR82

MR81

MR80

MR83

0

1

16-PIXEL

PORT CONTROL

DISABLE

ENABLE

DNR ENABLE

CONTROL

MR85

0

DISABLE

1

ENABLE

0

1

DISABLE

ENABLE

MR82

DOUBLE BUFFER

CONTROL

0

1

DISABLE

ENABLE

MR86

GAMMA ENABLE

CONTROL

0

1

CURVE A

CURVE B

MR87

GAMMA CURVE

SELECT CONTROL

ZERO SHOULD

BE WRITTEN

TO THIS BIT

MR81

0

1

DISABLE

ENABLE

MR80

PROGRESSIVE

SCAN CONTROL

Figure 64. Mode Register 8, MR8

相關PDF資料 |

PDF描述 |

|---|---|

| ADV7192 | Video Encoder with Six 10-Bit DACs, 54 MHz Oversampling and Progressive Scan Inputs |

| ADV7194KST | Professional Extended-10⑩ Video Encoder with 54 MHz Oversampling |

| ADV7194 | Professional Extended-10⑩ Video Encoder with 54 MHz Oversampling |

| ADV7202 | Simultaneous Sampling Video Rate Codec |

| ADV7300A | Multiformat SD, Progressive Scan/HDTV Video Encoder with Six NSV⑩ 12-Bit DACs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV7194 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Professional Extended-10⑩ Video Encoder with 54 MHz Oversampling |

| ADV7194KST | 制造商:Analog Devices 功能描述:Video Encoder 6DAC 10-Bit 80-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:PROFESSIONAL/HDTV NTSC/PAL ENCODER I.C. - Bulk 制造商:Analog Devices 功能描述:IC VIDEO ENCODER |

| ADV7194KSTZ | 功能描述:IC ENCODER VIDEO EXT-10 80-LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編碼器,解碼器,轉換器 系列:- 產品變化通告:Development Systems Discontinuation 26/Apr/2011 標準包裝:1 系列:- 類型:編碼器 應用:DVB-S.2 系統 電壓 - 電源,模擬:- 電壓 - 電源,數字:- 安裝類型:- 封裝/外殼:模塊 供應商設備封裝:模塊 包裝:散裝 其它名稱:Q4645799 |

| ADV7194KSTZ | 制造商:Analog Devices 功能描述:TV / Video IC |

| ADV7195 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs and 10-Bit Data Input |

發布緊急采購,3分鐘左右您將得到回復。