- 您現在的位置:買賣IC網 > PDF目錄374047 > ADV7341EBZ (Analog Devices, Inc.) Multiformat Video Encoder, Six 12-Bit Noise Shaped Video㈢ DACS PDF資料下載

參數資料

| 型號: | ADV7341EBZ |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Multiformat Video Encoder, Six 12-Bit Noise Shaped Video㈢ DACS |

| 中文描述: | 多格式視頻編碼器,6個12位噪聲整形視頻㈢交叉連接系統 |

| 文件頁數: | 57/88頁 |

| 文件大小: | 1066K |

| 代理商: | ADV7341EBZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁當前第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

ADV7340/ADV7341

DOUBLE BUFFERING

Subaddress 0x33, Bit 7 for ED/HD,

Subaddress 0x88, Bit 2 for SD

Double-buffered registers are updated once per field. Double

buffering improves overall performance because modifications

to register settings are not made during active video, but take

effect prior to the start of the active video on the next field.

Double buffering can be activated on the following ED/HD

registers using Subaddress 0x33, Bit 7: ED/HD Gamma A and

Gamma B curves, and ED/HD CGMS registers.

Double buffering can be activated on the following SD registers

using Subaddress 0x88, Bit 2: SD Gamma A and Gamma B

curves, SD Y scale, SD Cr scale, SD Cb scale, SD brightness, SD

closed captioning, and SD Macrovision Bits[5:0] (Subaddress

0xE0, Bits[5:0]).

PROGRAMMABLE DAC GAIN CONTROL

Subaddress 0x0A to Subaddress 0x0B

It is possible to adjust the DAC output signal gain up or down

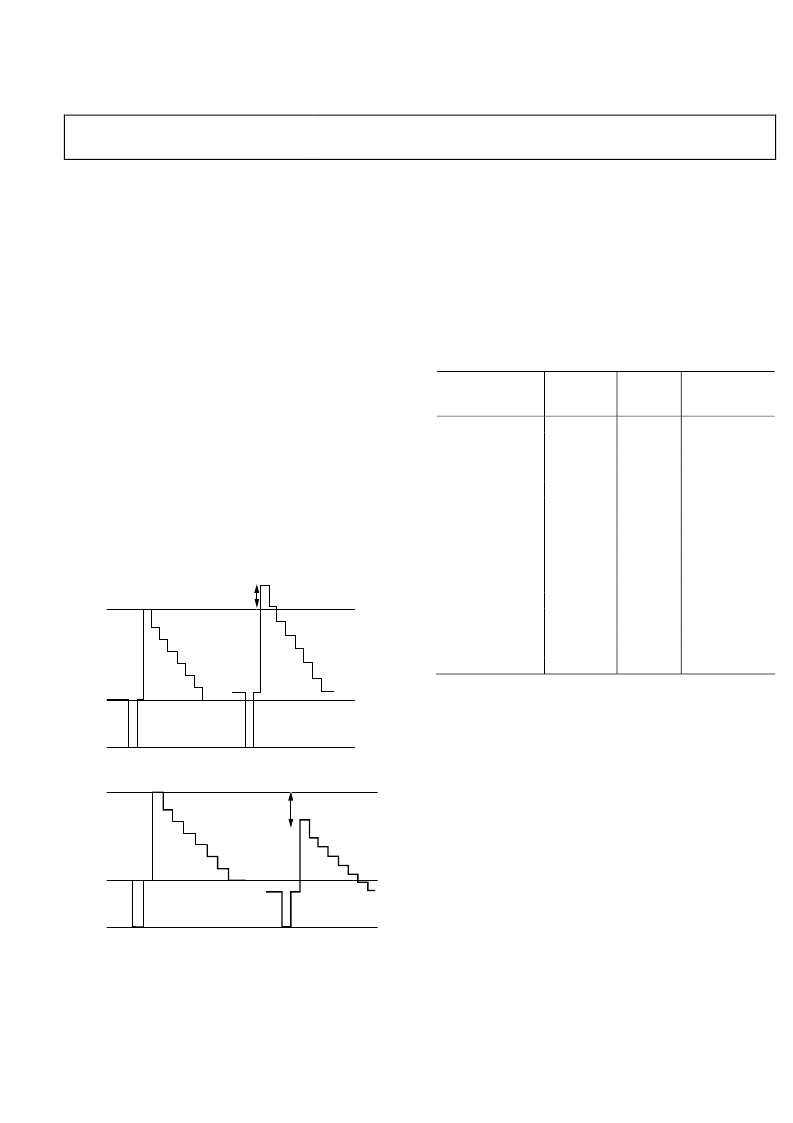

from its absolute level. This is illustrated in Figure 69.

DAC 4 to DAC 6 are controlled by Register 0x0A.

DAC 1 to DAC 3 are controlled by Register 0x0B.

Rev. 0 | Page 57 of 88

CASE B

700mV

300mV

NEGATIVE GAIN PROGRAMMED IN

DAC OUTPUT LEVEL REGISTERS,

SUBADDRESS 0x0A, 0x0B

CASE A

GAIN PROGRAMMED IN DAC OUTPUT LEVEL

REGISTERS, SUBADDRESS 0x0A, 0x0B

700mV

300mV

0

Figure 69. Programmable DAC Gain—Positive and Negative Gain

In Case A of Figure 69, the video output signal is gained. The

absolute level of the sync tip and blanking level both increase

with respect to the reference video output signal. The overall

gain of the signal is increased from the reference signal.

In Case B of Figure 69, the video output signal is reduced. The

absolute level of the sync tip and blanking level both decrease

with respect to the reference video output signal. The overall

gain of the signal is reduced from the reference signal.

The range of this feature is specified for ±7.5% of the nominal

output from the DACs. For example, if the output current of the

DAC is 4.33 mA, the DAC gain control feature can change this

output current from 4.008 mA (7.5%) to 4.658 mA (+7.5%).

The reset value of the control registers is 0x00, that is, nominal

DAC current is output. Table 46 is an example of how the

output current of the DACs varies for a nominal 4.33 mA

output current.

Table 46. DAC Gain Control

Reg. 0x0A or

Reg.0x0B

0100 0000 (0x40)

0011 1111 (0x3F)

0011 1110 (0x3E)

...

...

0000 0010 (0x02)

0000 0001 (0x01)

0000 0000 (0x00)

DAC

Current

(mA)

4.658

4.653

4.648

...

...

4.43

4.38

4.33

% Gain

7.5000%

7.3820%

7.3640%

...

...

0.0360%

0.0180%

0.0000%

Note

Reset value,

nominal

1111 1111 (0xFF)

1111 1110 (0xFE)

...

...

1100 0010 (0xC2)

1100 0001 (0xC1)

1100 0000 (0xC0)

GAMMA CORRECTION

Subaddress 0x44 to Subaddress 0x57 for ED/HD,

Subaddress 0xA6 to Subaddress 0xB9 for SD

Generally, gamma correction is applied to compensate for the

nonlinear relationship between signal input and output

brightness level (as perceived on a CRT). It can also be applied

wherever nonlinear processing is used.

Gamma correction uses the function

Signal

OUT

= (

Signal

IN

)

γ

where γ = is the gamma correction factor.

Gamma correction is available for SD and ED/HD video. For

both variations, there are 20, 8-bit registers. They are used to

program the Gamma Correction Curve A and Gamma

Correction Curve B.

ED/HD gamma correction is enabled using Subaddress 0x35,

Bit 5. ED/HD Gamma Correction Curve A is programmed at

Subaddress 0x44 to Subaddress 0x4D, and ED/HD Gamma

Correction Curve B is programmed at Subaddress 0x4E to

Subaddress 0x57.

4.25

4.23

...

...

4.018

4.013

4.008

0.0180%

0.0360%

...

...

7.3640%

7.3820%

7.5000%

相關PDF資料 |

PDF描述 |

|---|---|

| ADV7343BSTZ | Multiformat Video Encoder Six, 11-Bit, 297 MHz DACs |

| ADV7342 | Multiformat Video Encoder Six, 11-Bit, 297 MHz DACs |

| ADV7342BSTZ | Multiformat Video Encoder Six, 11-Bit, 297 MHz DACs |

| ADV7343 | Multiformat Video Encoder Six, 11-Bit, 297 MHz DACs |

| ADV7344 | Multiformat Video Encoder Six 14-Bit Noise Shaped Video DACs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV7342 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Video Encoder Six, 11-Bit, 297 MHz DACs |

| ADV7342BSTZ | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Video Encoder Six, 11-Bit, 297 MHz DACs |

| ADV7343 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Video Encoder Six, 11-Bit, 297 MHz DACs |

| ADV7343BSTZ | 功能描述:IC ENCODER VIDEO W/DAC 64-LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編碼器,解碼器,轉換器 系列:- 產品變化通告:Development Systems Discontinuation 26/Apr/2011 標準包裝:1 系列:- 類型:編碼器 應用:DVB-S.2 系統 電壓 - 電源,模擬:- 電壓 - 電源,數字:- 安裝類型:- 封裝/外殼:模塊 供應商設備封裝:模塊 包裝:散裝 其它名稱:Q4645799 |

| ADV7343WBSTZ | 功能描述:IC ENCODER VID 12BIT DAC 64LQFP 制造商:analog devices inc. 系列:- 包裝:托盤 零件狀態:在售 類型:視頻編碼器 應用:DVD,Blu-Ray 電壓 - 電源,模擬:2.6 V ~ 3.46 V 電壓 - 電源,數字:1.71 V ~ 1.89 V 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商器件封裝:64-LQFP(10x10) 標準包裝:1 |

發布緊急采購,3分鐘左右您將得到回復。