- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374047 > ADV7343BSTZ (ANALOG DEVICES INC) Multiformat Video Encoder Six, 11-Bit, 297 MHz DACs PDF資料下載

參數(shù)資料

| 型號: | ADV7343BSTZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | DAC |

| 英文描述: | Multiformat Video Encoder Six, 11-Bit, 297 MHz DACs |

| 中文描述: | SERIAL INPUT LOADING, 11-BIT DAC, QFP64 |

| 封裝: | ROHS COMPLIANT, MS-026BCD, LQFP-64 |

| 文件頁數(shù): | 45/88頁 |

| 文件大小: | 1053K |

| 代理商: | ADV7343BSTZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

ADV7342/ADV7343

Rev. 0 | Page 45 of 88

MPEG2

DECODER

CLKIN_A

S[7:0] OR Y[7:0]*

27MHz

YCrCb

ADV7342/

ADV7343

*SELECTED BY SUBADDRESS 0x01, BIT 7.

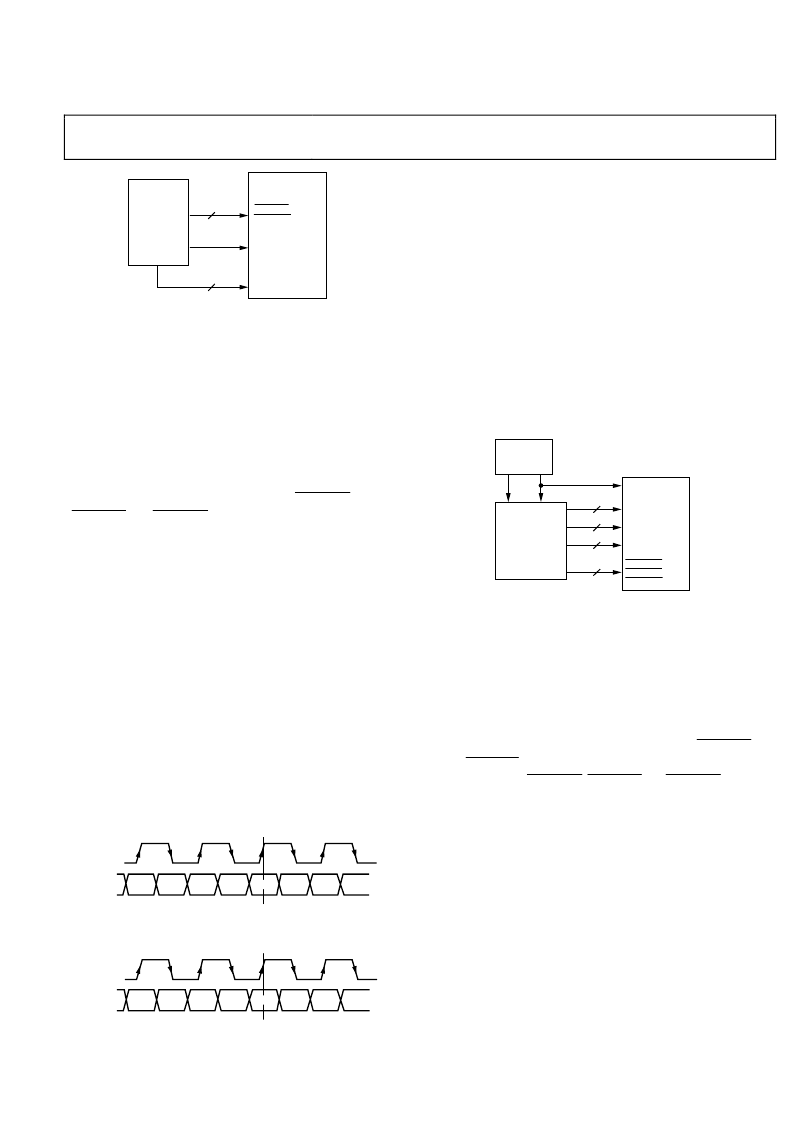

Figure 51. SD Only Example Application

S_VSYNC,

S_HSYNC

2

10

0

ENHANCED DEFINITION/HIGH DEFINITION ONLY

Subaddress 0x01, Bits[6:4] = 001 or 010

Enhanced definition (ED) or high definition (HD) YCrCb data

can be input in either 4:2:2 or 4:4:4 formats. If desired, dual data

rate (DDR) pixel data inputs can be employed (4:2:2 format only).

Enhanced definition (ED) or high definition (HD) RGB data

can be input in 4:4:4 format (single data rate only).

The clock signal must be provided on the CLKIN_A pin. Input

synchronization signals are provided on the P_HSYNC,

P_VSYNC, and P_BLANK pins.

16-Bit 4:2:2 YCrCb Mode (SDR)

Subaddress 0x35, Bit 1 = 0; Subaddress 0x33, Bit 6 = 1

In 16-bit 4:2:2 YCrCb input mode, the Y pixel data is

input on Pin Y7 to Pin Y0, with Y0 being the LSB.

The CrCb pixel data is input on Pin C7 to Pin C0, with C0

being the LSB.

8-Bit 4:2:2 YCrCb Mode (DDR)

Subaddress 0x35, Bit 1 = 0; Subaddress 0x33, Bit 6 = 1

In 8-bit DDR 4:2:2 YCrCb input mode, the Y pixel data is input

on Pin Y7 to Pin Y0 upon either the rising or falling edge of

CLKIN_A. Y0 is the LSB.

The CrCb pixel data is also input on Pin Y7 to Pin Y0

upon the opposite edge of CLKIN_A. Y0 is the LSB.

Whether the Y data is clocked in upon the rising or falling edge

of CLKIN_A is determined by Subaddress 0x01, Bits[2:1] (see

Figure 52 and Figure 53).

3FF

00

00

X

Y

Y0

Y1

Cr0

CLKIN_A

NOTES

1. SUBADDRESS 0x01 [2:1] SHOULD BE SET TO 00 IN THIS CASE.

Y[7:0]

Cb0

0

Figure 52. ED/HD-DDR Input Sequence (EAV/SAV)—Option A

3FF

00

00

XY

Cb0

Cr0

Y1

CLKIN_

A

Y[7:0]

Y0

NOTES

1. SUBADDRESS 0x01 [2:1] SHOULD BE SET TO11 IN THIS CASE.

0

Figure 53. ED/HD-DDR Input Sequence (EAV/SAV)—Option B

24-Bit 4:4:4 YCrCb Mode

Subaddress 0x35, Bit 1 = 0; Subaddress 0x33, Bit 6 = 0

In 24-bit 4:4:4 YCrCb input mode, the Y pixel data is input on

Pin Y7 to Pin Y0, with Y0 being the LSB.

The Cr pixel data is input on Pin S7 to Pin S0, with S0 being

the LSB.

The Cb pixel data is input on Pin C7 to Pin C0, with C0 being

the LSB.

24-Bit 4:4:4 RGB Mode

Subaddress 0x35, Bit 1 = 1

In 24-bit 4:4:4 RGB input mode, the red pixel data is input on

Pin S7 to Pin S0, the green pixel data is input on Pin Y7 to Pin

Y0, and the blue pixel data is input on Pin C7 to Pin C0. S0, Y0,

and C0 are the respective bus LSBs.

MPEG2

DECODER

CLKIN_

A

C[7:0]

S[7:0]

Y[7:0]

INTERLACED TO

PROGRESSIVE

YCrCb

P_VSYNC,

P_HSYNC,

P_BLANK

10

Cb

10

Cr

10

Y

3

0

ADV7342/

ADV7343

Figure 54. ED/HD Only Example Application

SIMULTANEOUS STANDARD DEFINITION AND

ENHANCED DEFINITION/HIGH DEFINITION

Subaddress 0x01, Bits[6:4] = 011 or 100

The ADV7342/ADV7343 are able to simultaneously process SD

4:2:2 YCrCb data and ED/HD 4:2:2 YCrCb data. The 27 MHz

SD clock signal must be provided on the CLKIN_A pin. The

ED/HD clock signal must be provided on the CLKIN_B pin. SD

input synchronization signals are provided on the S_HSYNC

and S_VSYNC pins. ED/HD input synchronization signals are

provided on the P_HSYNC, P_VSYNC and P_BLANK pins.

SD 8-Bit 4:2:2 YCrCb and ED/HD-SDR 16-Bit 4:2:2 YCrCb

The SD 8-bit 4:2:2 YCrCb pixel data is input on Pin S7 to Pin

S0, with S0 being the LSB.

The ED/HD 16-bit 4:2:2 Y pixel data is input on Pin Y7 to Pin

Y0, with Y0 being the LSB.

The ED/HD 16-bit 4:2:2 CrCb pixel data is input on Pin C7 to

Pin C0, with C0 being the LSB.

SD 8-Bit 4:2:2 YCrCb and ED/HD-DDR 8-Bit 4:2:2 YCrCb

The SD 8-bit 4:2:2 YCrCb pixel data is input on Pin S7 to Pin

S0, with S0 being the LSB.

The ED/HD-DDR 8-bit 4:2:2 Y pixel data is input on Pin Y7 to

Pin Y0 upon the rising or falling edge of CLKIN_B. Y0 is the LSB.

The ED/HD-DDR 8-bit 4:2:2 CrCb pixel data is also input on Pin

Y7 to Pin Y0 upon the opposite edge of CLKIN_B. Y0 is the LSB.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7342 | Multiformat Video Encoder Six, 11-Bit, 297 MHz DACs |

| ADV7342BSTZ | Multiformat Video Encoder Six, 11-Bit, 297 MHz DACs |

| ADV7343 | Multiformat Video Encoder Six, 11-Bit, 297 MHz DACs |

| ADV7344 | Multiformat Video Encoder Six 14-Bit Noise Shaped Video DACs |

| ADV7344BSTZ | Multiformat Video Encoder Six 14-Bit Noise Shaped Video DACs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7343WBSTZ | 功能描述:IC ENCODER VID 12BIT DAC 64LQFP 制造商:analog devices inc. 系列:- 包裝:托盤 零件狀態(tài):在售 類型:視頻編碼器 應用:DVD,Blu-Ray 電壓 - 電源,模擬:2.6 V ~ 3.46 V 電壓 - 電源,數(shù)字:1.71 V ~ 1.89 V 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商器件封裝:64-LQFP(10x10) 標準包裝:1 |

| ADV7343WBSTZ-RL | 功能描述:Video Encoder IC DVD, Blu-Ray 64-LQFP (10x10) 制造商:analog devices inc. 系列:- 包裝:帶卷(TR) 零件狀態(tài):有效 類型:視頻編碼器 應用:DVD,Blu-Ray 電壓 - 電源,模擬:2.6 V ~ 3.46 V 電壓 - 電源,數(shù)字:1.71 V ~ 1.89 V 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商器件封裝:64-LQFP(10x10) 標準包裝:1,500 |

| ADV7344 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Video Encoder Six 14-Bit Noise Shaped Video DACs |

| ADV7344BSTZ | 制造商:Analog Devices 功能描述: |

| ADV73505501 | 制造商:LG Corporation 功能描述:Frame Assembly |

發(fā)布緊急采購,3分鐘左右您將得到回復。