- 您現在的位置:買賣IC網 > PDF目錄374048 > ADV7401 (Analog Devices, Inc.) 10-Bit, Integrated, Multiformat SDTV/HDTV Video Decoder and RGB Graphics Digitizer PDF資料下載

參數資料

| 型號: | ADV7401 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 10-Bit, Integrated, Multiformat SDTV/HDTV Video Decoder and RGB Graphics Digitizer |

| 中文描述: | 10位,綜合,多格式標清/高清視頻解碼器和RGB圖形數字化儀 |

| 文件頁數: | 7/20頁 |

| 文件大小: | 242K |

| 代理商: | ADV7401 |

ADV7401

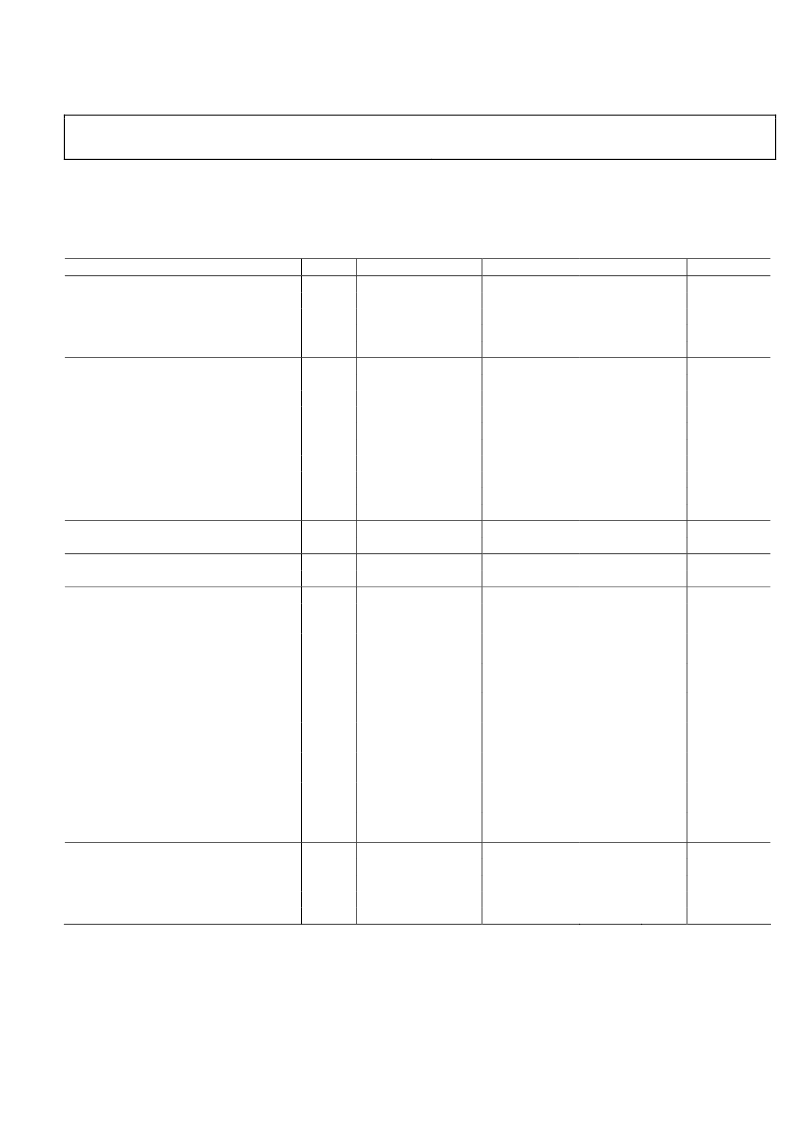

TIMING CHARACTERISTICS

@ AVDD = 3.15 V to 3.45 V, DVDD = 1.65 V to 2.0 V, DVDDIO = 3.0 V to 3.6 V, PVDD = 1.71 V to 1.89 V. Operating temperature range,

unless otherwise noted.

Table 3.

Parameter

1, ,

Symbol

Test Conditions

SYSTEM CLOCK AND CRYSTAL

Crystal Nominal Frequency

Crystal Frequency Stability

Horizontal Sync Input Frequency

LLC1 Frequency Range

4

I

2

C PORT

5

SCLK Frequency

SCLK Min Pulse Width High

t

1

SCLK Min Pulse Width Low

t

2

Hold Time (Start Condition)

t

3

Setup Time (Start Condition)

t

4

SDA Setup Time

t

5

SCLK and SDA Rise Time

t

6

SCLK and SDA Fall Time

t

7

Setup Time for Stop Condition

t

8

RESET FEATURE

Reset Pulse Width

CLOCK OUTPUTS

LLC1 Mark Space Ratio

t

9

:t

10

DATA and CONTROL OUTPUTS

Data Output Transition Time SDR (SDP)

6

t

11

Negative clock edge

to start of valid data

Data Output Transition Time SDR (SDP)

6

t

12

End of valid data to

negative clock edge

Data Output Transition Time SDR (CP)

7

t

13

End of valid data to

negative clock edge

Data Output Transition Time SDR (CP)

7

t

14

Negative clock edge

to start of valid data

Data Output Transition Time DDR (CP)

7, 8

t

15

Positive clock edge to

end of valid data

Data Output Transition Time DDR (CP)

7, 8

t

16

Positive clock edge to

start of valid data

Data Output Transition Time DDR (CP)

7, 8

t

17

Negative clock edge

to end of valid data

Data Output Transition Time DDR (CP)

7, 8

t

18

Negative clock edge

to start of valid data

DATA and CONTROL INPUTS

5

Input Setup Time (Digital Input Port)

t

19

HS_IN, VS_IN

DE_IN, data inputs

Input Hold Time (Digital Input Port)

t

20

HS_IN, VS_IN

DE_IN, data inputs

Rev. SpA | Page 7 of 20

2 3

Min

14.8

12.825

0.6

1.3

0.6

0.6

100

5

45:55

Typ

28.63636

0.6

Max

±50

110

140

400

300

300

55:45

3.6

Unit

MHz

ppm

kHz

MHz

kHz

μs

μs

μs

μs

ns

ns

ns

μs

ms

% duty cycle

ns

2.4

ns

2.8

ns

0.1

ns

4 + TLLC1/4

ns

0.25 + TLLC1/4

ns

2.95 + TLLC1/4

ns

0.5 + TLLC1/4

ns

9

2.2

7

2

ns

ns

ns

ns

1

The min/max specifications are guaranteed over this range.

2

Temperature range T

MIN

to T

MAX

: 40°C to +85°C (0°C to 70°C temperature range for ADV7401KSTZ-140).

3

Guaranteed by characterization.

4

Maximum LLC1 frequency is 80 MHz for ADV7401BSTZ-80 and is 110 MHz for ADV7401BSTZ-110.

5

TTL input values are 0 V to 3 V, with rise/fall times

≤

3 ns, measured between the 10% and 90% points.

6

SDP timing figures obtained using default drive strength value (0xD5) in Register Subaddress 0xF4.

7

CP timing figures obtained using max drive strength value (0xFF) in register subaddress 0xF4.

8

DDR timing specifications dependent on LLC1 output pixel clock; TLCC1/4 = 9.25 ns at LLC1 = 27 MHz.

相關PDF資料 |

PDF描述 |

|---|---|

| ADV7520NK | Low-Power HDMI/DVI Transmitter |

| ADV7520NKBBCZ-80 | Low-Power HDMI/DVI Transmitter |

| ADV7520NKBBCZRL-80 | Low-Power HDMI/DVI Transmitter |

| ADV7520NKBCPZ-801 | Low-Power HDMI/DVI Transmitter |

| ADVFC32 | Voltage-to-Frequency and Frequency-to-Voltage Converter |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV7401BSTZ-110 | 功能描述:視頻 IC 10-bit HD Video Decoder w/OSD & TTXT RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| ADV7401BSTZ-80 | 功能描述:視頻 IC 10-bit HD Video Decoder w/OSD & TTXT RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| ADV7401CSTZ-110 | 制造商:Analog Devices 功能描述: |

| ADV7401CSTZ-140 | 制造商:Analog Devices 功能描述: |

| ADV7401KSTZ-140 | 功能描述:視頻 IC 10-bit HD Video Decoder w/OSD & TTXT RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

發布緊急采購,3分鐘左右您將得到回復。