- 您現在的位置:買賣IC網 > PDF目錄379696 > ATT3020-50M44I (Electronic Theatre Controls, Inc.) Field-Programmable Gate Arrays PDF資料下載

參數資料

| 型號: | ATT3020-50M44I |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類: | FPGA |

| 英文描述: | Field-Programmable Gate Arrays |

| 中文描述: | 現場可編程門陣列 |

| 文件頁數: | 58/80頁 |

| 文件大小: | 528K |

| 代理商: | ATT3020-50M44I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁當前第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

Data Sheet

February 1997

ATT3000 Series Field-Programmable Gate Arrays

58

Lucent Technologies Inc.

Electrical Characteristics

(continued)

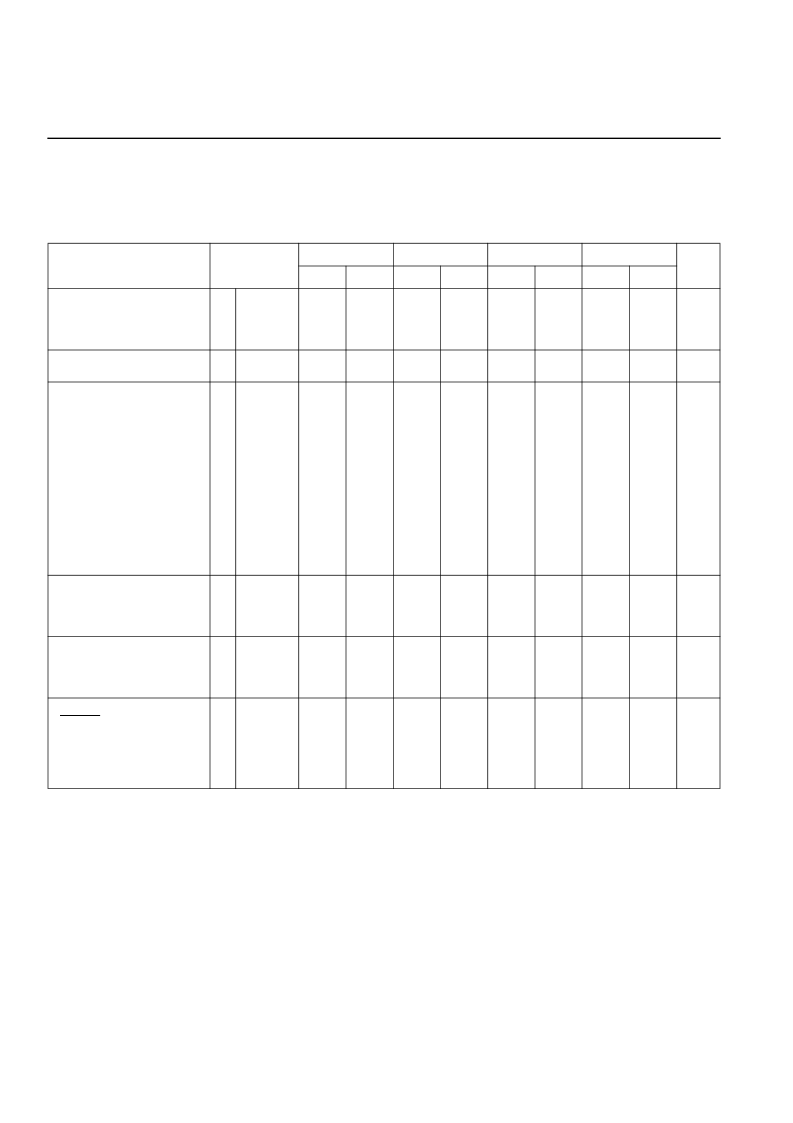

Table 22. IOB Switching Characteristics (-50, -70, -100, and -125)

* These parameters are for clock pulses within an FPGA device. For externally applied clock, increase values by 20%.

Notes:

Timing is measured at pin threshold with 50 pF external capacitive loads (including test fixture).

Typical fast mode output rise/fall times are 2 ns and will increase approximately 2%/pF of additional load.

Typical slew-rate limited output rise/fall times are approximately 4 times longer.

A maximum total external capacitive load for simultaneous fast mode switching in the same direction is 200 pF per power/ground pin pair. For

slew-rate limited outputs, this total is 4 times larger. Exceeding this maximum capacitive load can result in ground bounce of >1.5 V amplitude

and <5 ns duration, which may cause problems when the FPGA drives clocks and other asynchronous signals.

Voltage levels of unused (bonded and unbonded) pads must be valid logic levels. Each can be configured with the internal pull-up resistor or

alternatively configured as a driven output or driven from an external source.

Input pad setup time is specified with respect to the internal clock (ik).

To calculate system setup time, subtract clock delay (pad to ik) from the input pad setup time value. Input pad hold time with respect to the inter-

nal clock (ik) is negative. This means that pad levels changed immediately before the internal clock edge (ik) will not be recognized.

Commercial: V

CC

= 5.0 V ± 5%; 0 °C

≤

T

A

≤

70 °C; Industrial: V

CC

= 5.0 ± 10%, –40 °C

≤

T

A

≤

+85 °C.

Description

Symbol

-50

-70

-100

-125

Unit

Min

Max

Min

Max

Min

Max

Min

Max

Input Delays

Pad to Direct In

Pad to Registered In

Clock to Registered In

Setup Time (Input):

Clock Setup Time

Output Delays

Clock to Pad

Fast

Slew-rate Limited

Output to Pad

Fast

Slew-rate Limited

3-state to Pad Hi-Z

Fast

Slew-rate Limited

3-state to Pad Valid

Fast

Slew-rate Limited

Setup and Hold Times (out-

put)

Clock Setup Time

Clock Hold Time

Clock

High Time*

Low Time*

Max. Flip-Flop Toggle*

Master Reset Delays

RESET to:

Registered In

Output Pad (fast)

Output Pad (slew-

rate limited)

3

—

4

T

PID

T

PTG

T

IKRI

—

—

—

9.0

34.0

11.0

—

—

—

6.0

21.0

5.5

—

—

—

4.0

17.0

4.0

—

—

—

3.0

16.0

3.0

ns

ns

ns

1

T

PICK

30.0

—

20.0

—

17.0

—

16.0

—

ns

7

7

10

10

9

9

8

8

T

OKPO

T

OKPO

T

OPF

T

OPS

T

TSHZ

T

TSHZ

T

TSON

T

TSON

—

—

—

—

—

—

—

—

18.0

43.0

15.0

40.0

10.0

37.0

20.0

45.0

—

—

—

—

—

—

—

—

13.0

33.0

9.0

29.0

8.0

28.0

14.0

34.0

—

—

—

—

—

—

—

—

10.0

27.0

6.0

23.0

8.0

25.0

12.0

29.0

—

—

—

—

—

—

—

—

9.0

24.0

5.0

20.0

7.0

24.0

11.0

27.0

ns

ns

ns

ns

ns

ns

ns

ns

5

6

T

OCK

T

OKO

15.0

0

—

—

10.0

0

—

—

9.0

0

—

—

8.0

0

—

—

ns

ns

11

12

—

T

CH

T

CL

F

CLK

9.0

9.0

—

—

—

50

5.0

5.0

—

—

—

70

4.0

4.0

—

—

—

100

3.0

3.0

—

—

—

125

ns

ns

MHz

13

15

15

T

RRI

T

RPO

T

RPO

—

—

—

35

50

68

—

—

—

25

35

53

—

—

—

24

33

45

—

—

—

23

29

42

ns

ns

ns

相關PDF資料 |

PDF描述 |

|---|---|

| ATT3020-50M68I | Field-Programmable Gate Arrays |

| ATT3020-50M84I | Field-Programmable Gate Arrays |

| ATT3020-50S132I | Field-Programmable Gate Arrays |

| ATT3020-50S44I | Field-Programmable Gate Arrays |

| ATT3020-50S68I | Field-Programmable Gate Arrays |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ATT3020-50M68I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Gate Arrays |

| ATT3020-50M84I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Gate Arrays |

| ATT3020-50N100M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| ATT3020-50R84M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| ATT3020-50S132I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Gate Arrays |

發布緊急采購,3分鐘左右您將得到回復。