- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379700 > ATT3030-50M132I (Electronic Theatre Controls, Inc.) Field-Programmable Gate Arrays PDF資料下載

參數(shù)資料

| 型號(hào): | ATT3030-50M132I |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類: | FPGA |

| 英文描述: | Field-Programmable Gate Arrays |

| 中文描述: | 現(xiàn)場(chǎng)可編程門陣列 |

| 文件頁數(shù): | 65/80頁 |

| 文件大小: | 528K |

| 代理商: | ATT3030-50M132I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁當(dāng)前第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

Data Sheet

February 1997

ATT3000 Series Field-Programmable Gate Arrays

Lucent Technologies Inc.

65

Electrical Characteristics

(continued)

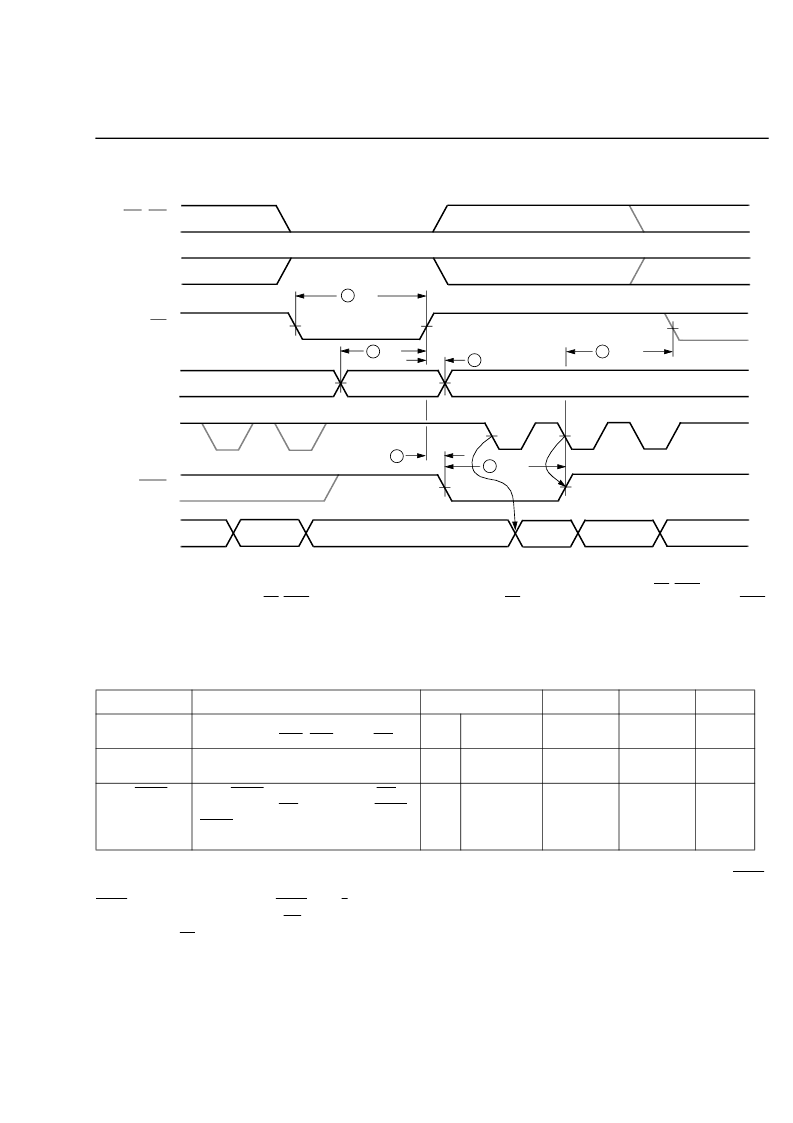

Note: The requirements in this timing diagram are extremely relaxed; data need not be held beyond the rising edge of

WS

.

BUSY

will go active

within 60 ns after the end of

WS

.

BUSY

will stay active for several microseconds.

WS

may be asserted immediately after the end of

BUSY

.

Figure 38. Peripheral Mode Switching Characteristics

Notes:

At powerup, V

CC

must rise from 2.0 V to V

CC

minimum in less than 25 ms. If this is not possible, configuration can be delayed by holding

RESET

low until V

CC

has reached 4.0 V. A very long V

CC

rise time of >100 ms, or a nonmonotonically rising V

CC

may require a >1 μs high level on

RESET

, followed by >6 μs low level on

RESET

and D/

P

after V

CC

has reached 4.0 V.

Configuration must be delayed until the

INIT

of all FPGAs is high.

Time from end of

WS

to CCLK cycle for the new byte of data depends on completion of previous byte processing and the phase of the

internal timing generator for CCLK.

CCLK and DOUT timing is tested in slave mode.

T

BUSY

indicates that the double-buffered parallel-to-serial converter is not yet ready to receive new data. The shortest T

BUSY

occurs when a

byte is loaded into an empty parallel-to-serial converter. The longest T

BUSY

occurs when a new word is loaded into the input register before the

second-level buffer has started shifting out data.

Table 28. Peripheral Mode Switching Characteristics

Signal

Write Signal

Description

Symbol

Min

Max

Unit

Effective Write Time Required

(Assertion of

CS0

,

CS1

, CS2,

WS

)

DIN Setup Time Required

DIN Hold TIme Required

RDY/

BUSY

Delay after End of

WS

Earliest Next

WS

after End of

BUSY

BUSY

Low Time Generated

1

2

3

4

5

6

T

CA

T

DC

T

CD

T

WTRB

T

RBWT

T

BUSY

100

60

0

—

0

2.5

—

—

—

60

—

9

ns

ns

ns

ns

ns

D[7:0]

RDY/

BUSY

CCLK

Periods

5-3129(F)

CS1/CS0

CS2

WS

D[7:0]

CCLK

RDY/BUSY

DOUT

T

CA

T

DC

T

CD

VALID

T

RBWT

T

WTRB

T

BUSY

GROUP OF

8 CCLKs

1

4

3

6

5

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ATT3030-50M44I | Field-Programmable Gate Arrays |

| ATT3030-50M68I | Field-Programmable Gate Arrays |

| ATT3030-50M84I | Field-Programmable Gate Arrays |

| ATT3030-50S132I | Field-Programmable Gate Arrays |

| ATT3030-50S44I | Field-Programmable Gate Arrays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ATT3030-50M44I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Gate Arrays |

| ATT3030-50M68I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Gate Arrays |

| ATT3030-50M84I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Gate Arrays |

| ATT3030-50S132I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Gate Arrays |

| ATT3030-50S44I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。