- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄352635 > BUS-61555-49Z Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號(hào): | BUS-61555-49Z |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項(xiàng)-數(shù)據(jù)表參考 |

| 文件頁(yè)數(shù): | 1/4頁(yè) |

| 文件大小: | 49K |

| 代理商: | BUS-61555-49Z |

DDC’s

BUS-61553

Advanced

Integrated Mux (AIM) Hybrid is a

complete

MIL-STD-1553

Bus

Controller (BC), Remote Terminal

Unit (RTU), and Bus Monitor (MT)

device. Packaged in a single 78-pin

DIP package, the BUS-61553 con-

tains dual low-power transceivers,

complete BC/RT/MT protocol logic, a

MIL-STD-1553-to-host interface unit

and 8K x 16 RAM.

Using an industry standard dual

transceiver and standard status and

control signals, the BUS-61553 sim-

plifies system integration at both the

MIL-STD-1553 and host processor

interface levels.

All 1553 operations are controlled

through the CPU access to the

shared 8K x 16 RAM. To ensure

maximum design flexibility, memory

control lines are provided for attach-

ing external RAM to the BUS-61553

address and data buses and for dis-

abling internal memory; the total

combined memory space can be

expanded to 64K x 16. All 1553 trans-

fers are entirely memory-mapped;

thus the CPU interface requires

minimal hardware and/or software

support.

The BUS-61553 operates over the

full military -55°C to +125°C temper-

ature range. Available screened to

MIL-PRF-38534, the BUS-61553 is

ideal for demanding military and

industrial

microprocessor-to-1553

interface applications.

DESCRIPTION

MIL-STD-1553 ADVANCED INTEGRATED

MUX (AIM) HYBRID

FEATURES

Fully Intergrated Terminal

Including:

–Dual Transceiver

–BC/RT/MT Protocol

–Memory Management Unit

–Processor lnterface Logic

–8K x 16 RAM

CMOS and Bipolar Technologies

Internal Interrupt Status and Time

Tag Registers

High Reliability

883B Processing Available

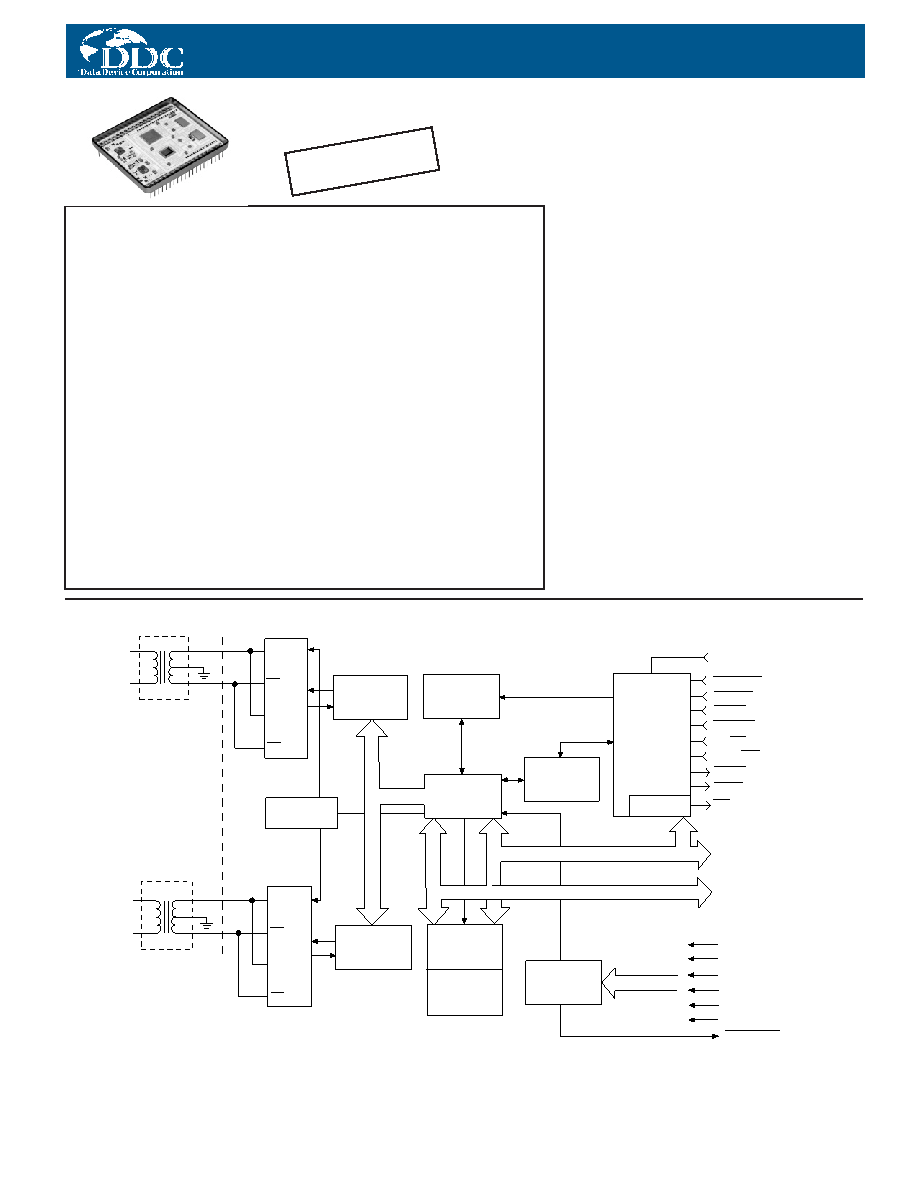

DATA

BUS A

TRANSFORMER A

BUS-25679

8

4

1

2

3

BUS-25679

DATA

BUS B

TRANSFORMER B

8

4

3

2

1

TX

RX

TRANSCEIVER B

INH

768

s

TIME OUT

TX

RX

INH

TRANSCEIVER A

CHANNEL A

ENCODER/

DECODER

MEMORY

TIMING

PROTOCOL

CONTROLLER

CHANNEL B

ENCODER/

DECODER

8K x 16

SHARED RAM

RAM

PARITY

CHECKER

RT ADDR

RTPARERR

RTAD P

RTAD4

RTAD3

RTAD2

RTAD1

RTAD0

INT

EXTLD

EXTEN

MEM/REG

RD/WR

READYD

STRBD

SELECT

MSTRCLR

CLOCK IN

INTERRUPT

GENERATOR

CPU

TIMING

D15-D00

A15-A00

CONTENTION

RESOLVER

FIGURE 1. BU-61553 BLOCK DIAGRAM

SEE ALSO

USER’S

GUIDE

BUS-61553

1987, 1999 Data Device Corporation

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BUS-61555-50 | Controller Miscellaneous - Datasheet Reference |

| BUS-61555-52K | Controller Miscellaneous - Datasheet Reference |

| BUS-61555-52L | Controller Miscellaneous - Datasheet Reference |

| BUS-61555-52Q | Controller Miscellaneous - Datasheet Reference |

| BUS-61555-52S | Controller Miscellaneous - Datasheet Reference |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BUS-61555-50 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| BUS-61555-50K | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| BUS-61555-50L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| BUS-61555-50Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| BUS-61555-50S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。