- 您現在的位置:買賣IC網 > PDF目錄366628 > C9821GQ Up to 5A ULDO linear regulator PDF資料下載

參數資料

| 型號: | C9821GQ |

| 英文描述: | Up to 5A ULDO linear regulator |

| 中文描述: | 單時鐘驅動器| SSOP封裝| 24針|塑料 |

| 文件頁數: | 1/18頁 |

| 文件大小: | 121K |

| 代理商: | C9821GQ |

Direct Rambus

Plus Clock Generator

Cypress Semiconductor Corporation

525 Los Coches St.

Milpitas, CA 95035. Tel: 408-263-6300, Fax: 408-263-6571

http://www.cypress.com

Document#: 38-07092 Rev. **

05/03/2001

Page 1 of 18

APPROVED PRODUCT

C9821

Product Features

High Speed Clock support - provides a 267 to

400MHz differential clock source for Direct

Rambus

memory systems for an 1.6 GbPS

data transfer rate

Synchronization Flexibility - provides signals to

synchronize the clock domains of the Rambus

Channel with an external system or processor

clock, provided by C9801, C9812, C9830,

C9840, C9850, C9851, and the C9853.

Power Management Support permits channel

clocks to be enabled and disabled as required

Supports Independent Channel Clocking

24 pin 150 mil SSOP Package

Supports Intel Architecture platforms

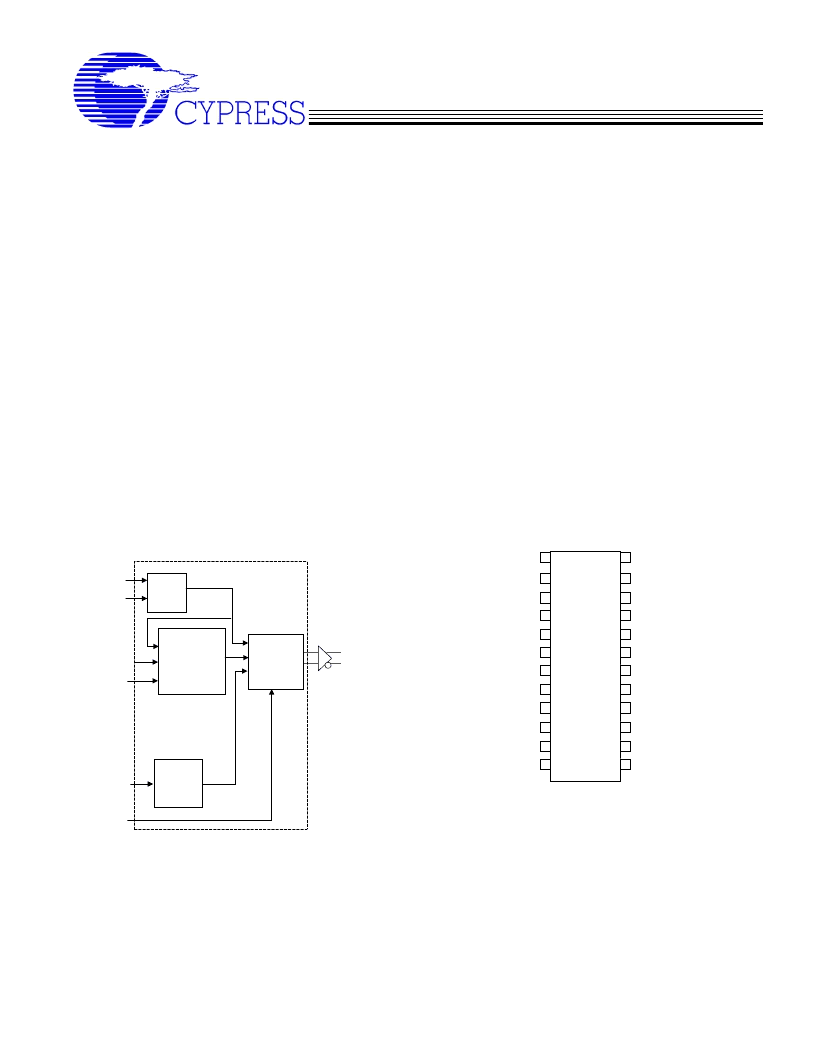

Block Diagram

PLL

Phase

Aligner

Test

Logic

REFCLK

MULT 0:1

PCLKM

SYNCLKN

S0:2

STOPB

CLK

CLKB

Output

Control

Logic

Figure: 1

Product Description

The C9821 is a Rambus

compliant DRCG clock

synchronizer. It contains a Phase Locked Loop that

provides complimentary Rambus

memory clocks.

Included in its functionality is the control logic to

phase and frequency synchronizing the device’s

output clocks with the system reference clock. Power

management logic is also provided for Mobile

application and green PC functionality. Also included

are separate power pins for each internal functional

block so as to minimize interaction of these sections

with each other and thus maximize the device

performance.

Pin Configuration

VddlR

Refclk

VddP

VssP

VssI

PclkM

SynClkN

VssC

VddC

VddlPD

StopB

PwrDnB

S0

S1

VddO

VssO

Clk

N/C

ClkB

VssO

VddO

Mult0

Mult1

S2

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

Figure: 2

相關PDF資料 |

PDF描述 |

|---|---|

| C9822EQ | Up to 5A ULDO linear regulator |

| C9827JT | Up to 5A ULDO linear regulator |

| C9827JY | Up to 5A ULDO linear regulator |

| C9832HT | Up to 5A ULDO linear regulator |

| C9832HY | N-CHANNEL 60V - 0.014 Ohm - 60A TO-220/TO220FP STRIPFET POWER MOSFET |

相關代理商/技術參數 |

參數描述 |

|---|---|

| C9822EQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE CLOCK DRIVER|SSOP|24PIN|PLASTIC |

| C98-24379-02 | 制造商:CPI 功能描述: |

| C9827H | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:High Performance Pentium 4 Clock Synthesizer |

| C9827HT | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:High Performance Pentium 4 Clock Synthesizer |

| C9827HY | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:High Performance Pentium 4 Clock Synthesizer |

發布緊急采購,3分鐘左右您將得到回復。