- 您現在的位置:買賣IC網 > PDF目錄379724 > CA3045 (HARRIS SEMICONDUCTOR) General Purpose NPN Transistor Arrays PDF資料下載

參數資料

| 型號: | CA3045 |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 小信號晶體管 |

| 英文描述: | General Purpose NPN Transistor Arrays |

| 中文描述: | 5 CHANNEL, VHF BAND, Si, NPN, RF SMALL SIGNAL TRANSISTOR |

| 文件頁數: | 1/6頁 |

| 文件大小: | 53K |

| 代理商: | CA3045 |

1

CA3045, CA3046

General Purpose NPN Transistor Arrays

The CA3045 and CA3046 each consist of five general

purpose silicon NPN transistors on a common monolithic

substrate. Two of the transistors are internally connected to

form a differentially connected pair.

The transistors of the CA3045 and CA3046 are well suited to

a wide variety of applications in low power systems in the DC

through VHF range. They may be used as discrete

transistors in conventional circuits. However, in addition, they

provide the very significant inherent integrated circuit

advantages of close electrical and thermal matching.

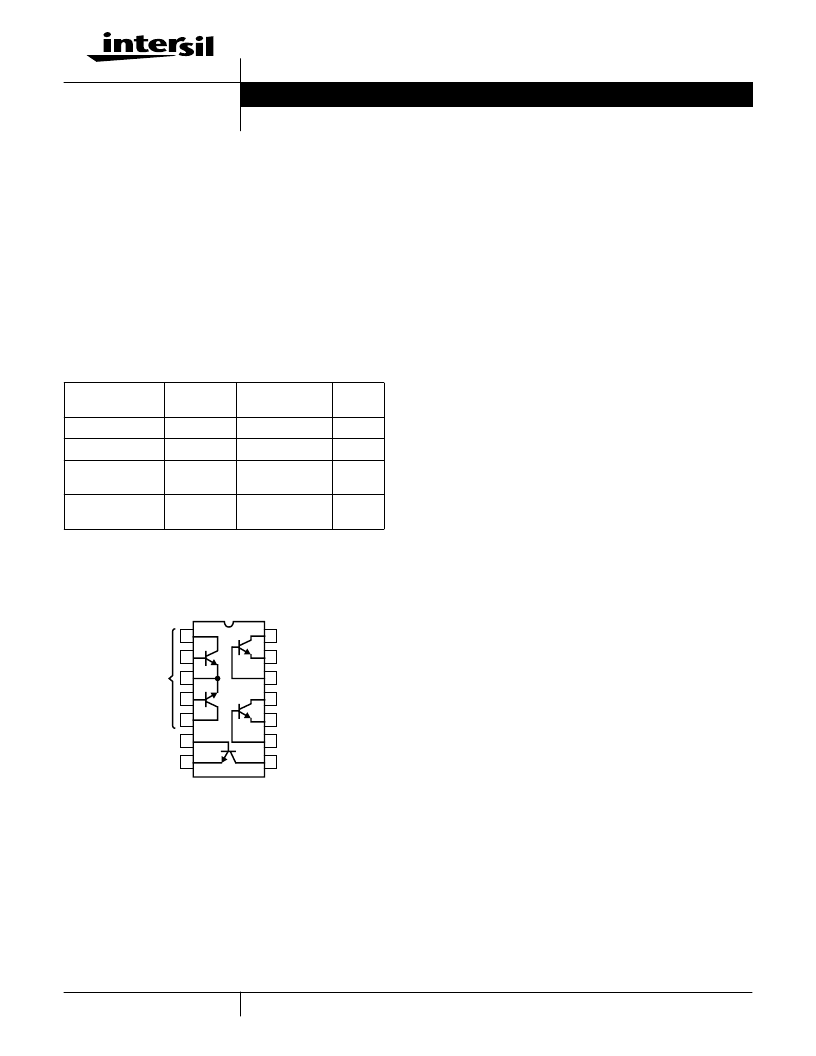

Pinout

CA3045, (CERDIP)

CA3046 (PDIP, SOIC)

TOP VIEW

Features

Two Matched Transistors

- V

BE

Match . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

±

5mV

- I

IO

Match. . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

μ

A (Max)

Low Noise Figure . . . . . . . . . . . . . . . . 3.2dB (Typ) at 1kHz

5 General Purpose Monolithic Transistors

Operation From DC to 120MHz

Wide Operating Current Range

Full Military Temperature Range

Applications

Three Isolated Transistors and One Differentially

Connected Transistor Pair for Low Power Applications at

Frequencies from DC Through the VHF Range

Custom Designed Differential Amplifiers

Temperature Compensated Amplifiers

See Application Note, AN5296 “Application of the CA3018

Integrated-Circuit Transistor Array” for Suggested

Applications

Ordering Information

PART NUMBER

(BRAND)

TEMP.

RANGE (

o

C)

PACKAGE

PKG.

NO.

CA3045F

-55 to 125

14 Ld CERDIP

F14.3

CA3046

-55 to 125

14 Ld PDIP

E14.3

CA3046M

(3046)

-55 to 125

14 Ld SOIC

M14.15

CA3046M96

(3046)

-55 to 125

14 Ld SOIC Tape

and Reel

M14.15

SUBSTRATE

1

2

3

4

5

6

7

14

13

12

11

10

9

8

DIFFERENTIAL

PAIR

Q

1

Q

5

Q

4

Q

3

Q

2

Data Sheet

September 1998

File Number

341.4

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

|

Copyright

Intersil Corporation 1999

相關PDF資料 |

PDF描述 |

|---|---|

| CA3045F | General Purpose NPN Transistor Arrays |

| CA3046 | General Purpose NPN Transistor Arrays |

| CA3046M | General Purpose NPN Transistor Arrays |

| CA3046M96 | General Purpose NPN Transistor Arrays |

| CA3054MZ96 | Dual Independent Differential Amp for Low Power Applications from DC to 120MHz |

相關代理商/技術參數 |

參數描述 |

|---|---|

| CA3045 DIE | 制造商:Harris Corporation 功能描述: |

| CA3045 WAF | 制造商:Harris Corporation 功能描述: |

| CA3045F | 制造商:RCA 功能描述: 制造商:Harris Corporation 功能描述:Bipolar Junction Transistor, Array, DIP 制造商:RCA 功能描述:Bipolar Junction Transistor, Array, DIP |

| CA3045F/883 | 制造商:Raytheon 功能描述: |

| CA3045F/883B | 制造商: 功能描述: 制造商:Raytheon 功能描述: 制造商:undefined 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。