- 您現在的位置:買賣IC網 > PDF目錄353028 > CY2308ZXC-5H (Cypress Semiconductor Corp.) 3.3V Zero Delay Buffer PDF資料下載

參數資料

| 型號: | CY2308ZXC-5H |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 3.3V Zero Delay Buffer |

| 中文描述: | 3.3零延遲緩沖器 |

| 文件頁數: | 1/14頁 |

| 文件大小: | 203K |

| 代理商: | CY2308ZXC-5H |

3.3V Zero Delay Buffer

CY2308

Cypress Semiconductor Corporation

3901 North First Street

San Jose

CA 95134

408-943-2600

Document #: 38-07146 Rev. *C

Revised June 16, 2004

1CY2308

Features

Zero input-output propagation delay, adjustable by

capacitive load on FBK input

Multiple configurations, see “Available CY2308

Configurations” table

Multiple low-skew outputs

— Output-output skew less than 200 ps

— Device-device skew less than 700 ps

— Two banks of four outputs, three-stateable by two

select inputs

10-MHz to 133-MHz operating range

Low jitter, less than 200 ps cycle-cycle (–1, –1H, –4, –5H)

Space-saving 16-pin 150-mil SOIC package or 16-pin

TSSOP

3.3V operation

Industrial Temperature available

Functional Description

The CY2308 is a 3.3V Zero Delay Buffer designed to distribute

high-speed clocks in PC, workstation, datacom, telecom, and

other high-performance applications.

The part has an on-chip PLL which locks to an input clock

presented on the REF pin. The PLL feedback is required to be

driven into the FBK pin, and can be obtained from one of the

outputs. The input-to-output skew is guaranteed to be less

than 350 ps, and output-to-output skew is guaranteed to be

less than 200 ps.

The CY2308 has two banks of four outputs each, which can

be controlled by the Select inputs as shown in the table “Select

Input Decoding.” If all output clocks are not required, Bank B

can be three-stated. The select inputs also allow the input

clock to be directly applied to the output for chip and system

testing purposes.

The CY2308 PLL enters a power-down state when there are

no rising edges on the REF input. In this mode, all outputs are

three-stated and the PLL is turned off, resulting in less than

50

A of current draw. The PLL shuts down in two additional

cases as shown in the “Select Input Decoding” table.

Multiple CY2308 devices can accept the same input clock and

distribute it in a system. In this case, the skew between the

outputs of two devices is guaranteed to be less than 700 ps.

The CY2308 is available in five different configurations, as

shown in the “Available CY2308 Configurations” table on page

2. The CY2308–1 is the base part, where the output

frequencies equal the reference if there is no counter in the

feedback path. The CY2308–1H is the high-drive version of

the –1, and rise and fall times on this device are much faster.

The CY2308–2 allows the user to obtain 2X and 1X

frequencies on each output bank. The exact configuration and

output frequencies depends on which output drives the

feedback pin. The CY2308–3 allows the user to obtain 4X and

2X frequencies on the outputs.

The CY2308–4 enables the user to obtain 2X clocks on all

outputs. Thus, the part is extremely versatile, and can be used

in a variety of applications.

The CY2308–5H is a high-drive version with REF/2 on both

banks.

9

16

FBK

CLKA4

CLKA3

VDD

GND

CLKB4

CLKB3

S1

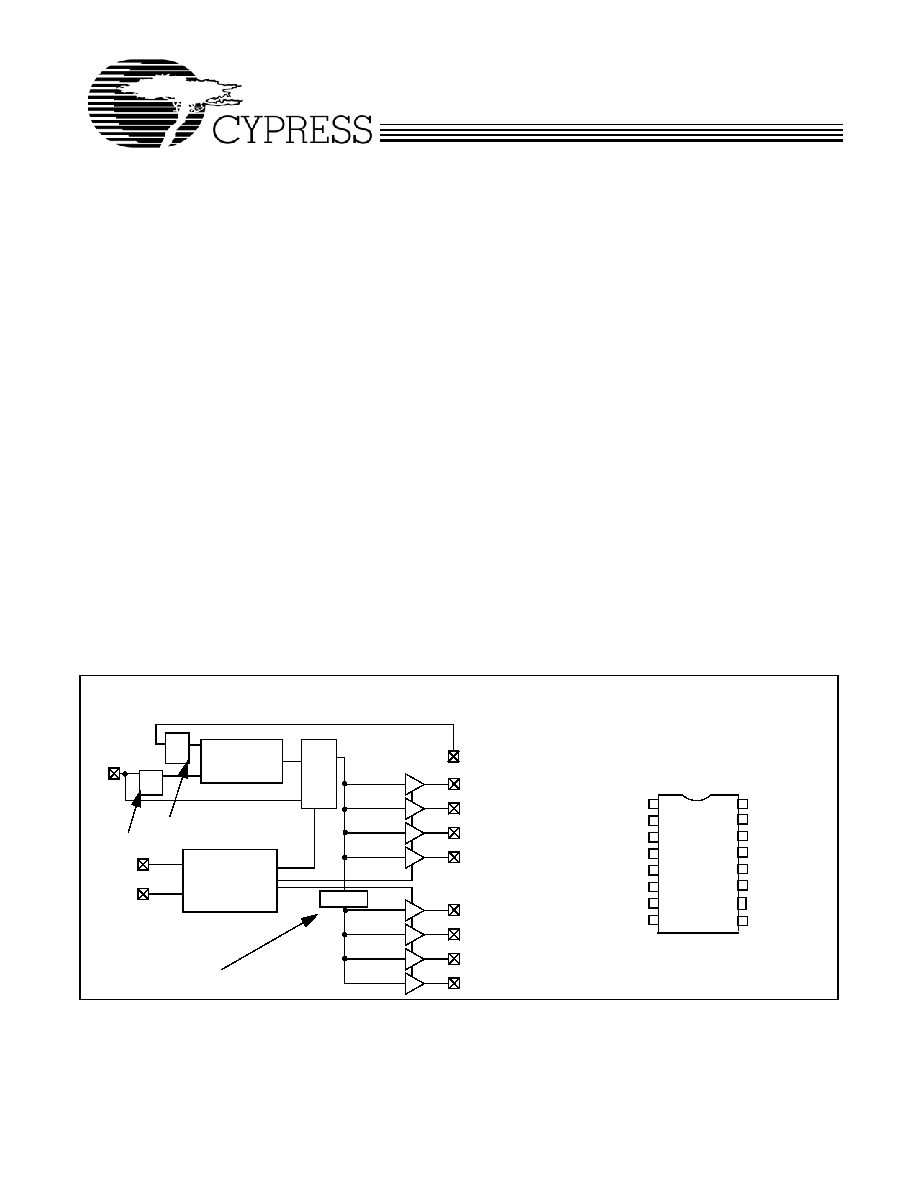

Block Diagram

1

2

3

4

5

6

7

8

10

11

12

13

14

15

REF

CLKA1

CLKA2

VDD

GND

CLKB1

CLKB2

S2

SOIC

Top View

Pin Configuration

REF

CLKA1

CLKA2

CLKA3

CLKA4

FBK

PLL

MUX

Select Input

Decoding

S2

S1

CLKB1

CLKB2

CLKB3

CLKB4

/2

Extra Divider (–2, –3)

/2

Extra Divider (–3, –4)

Extra Divider (–5H)

/2

相關PDF資料 |

PDF描述 |

|---|---|

| CY7C1069AV33-10BAI | 2M x 8 Static RAM |

| CY7C1069AV33-10ZC | 2M x 8 Static RAM |

| CY7C1069AV33-10ZI | 2M x 8 Static RAM |

| CY7C1069AV33-12BAC | 2M x 8 Static RAM |

| CY7C1069AV33-12BAI | 2M x 8 Static RAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| CY2308ZXI-1H | 功能描述:時鐘緩沖器 3.3VZDB COM RoHS:否 制造商:Texas Instruments 輸出端數量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| CY2308ZXI-1HT | 功能描述:時鐘緩沖器 3.3VZDB COM RoHS:否 制造商:Texas Instruments 輸出端數量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| CY2308ZXI-5H | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:3.3V Zero Delay Buffer |

| CY2309 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Low-Cost 3.3V Zero Delay Buffer |

| CY2309C | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:3.3V Zero Delay Clock Buffer |

發布緊急采購,3分鐘左右您將得到回復。