- 您現在的位置:買賣IC網 > PDF目錄380136 > CY39100V388-125BGI (Cypress Semiconductor Corp.) CPLDs at FPGA Densities PDF資料下載

參數資料

| 型號: | CY39100V388-125BGI |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | CPLDs at FPGA Densities |

| 中文描述: | CPLD器件在FPGA的密度 |

| 文件頁數: | 1/86頁 |

| 文件大小: | 1235K |

| 代理商: | CY39100V388-125BGI |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁

CPLDs at FPGA Densities

Carry-chain logic for fast and efficient arithmetic opera-

tions

Multiple I/O standards supported

—LVCMOS (3.3/3.0/2.5/1.8V), LVTTL, 3.3V PCI, SSTL2

(I-II), SSTL3 (I-II), HSTL (I-IV), and GTL+

Compatible with NOBL, ZBT, and QDR SRAMs

Programmable slew rate control on each I/O pin

User-programmable Bus Hold capability on each I/O pin

Fully 3.3V PCI-compliant (to 66-MHz 64-bit PCI spec,

rev. 2.2)

CompactPCI hot swap ready

Multiple package/pinout offering across all densities

—208 to 676 pins in PQFP, BGA, and FBGA packages

—Simplifies design migration across density

—Self-Boot solution in BGA and FBGA packages

In-System Reprogrammable (ISR)

—JTAG-compliant on-board programming

—Design changes do not cause pinout changes

IEEE1149.1 JTAG boundary scan

Delta39K ISR

CPLD Family

Cypress Semiconductor Corporation

Document #: 38-03039 Rev. *H

3901 North First Street

San Jose

CA 95134

408-943-2600

Revised August 1, 2003

Features

High density

—30K to 200K usable gates

—512 to 3072 macrocells

—136 to 428 maximum I/O pins

—Twelve dedicated inputs including four clock pins,

four global I/O control signal pins and four JTAG

interface pins for boundary scan and reconfig-

urability

Embedded memory

—80K to 480K bits embedded SRAM

16K to 96K bits of (dual-port) channel memory

High speed – 233-MHz in-system operation

AnyVolt

interface

—3.3V, 2.5V,1.8V, and 1.5V I/O capability

Low-power operation

—0.18-mm six-layer metal SRAM-based logic process

—Full-CMOS implementation of product term array

—Standby current as low as 5mA

Simple timing model

—No penalty for using full 16 product terms/macrocell

—No delay for single product term steering or sharing

Flexible clocking

—Spread Aware PLL drives all four clock networks

Allows 0.6% spread spectrum input clocks

Several multiply, divide and phase shift options

—Four synchronous clock networks per device

—Locally generated product term clock

—Clock polarity control at each register

Development Software

Warp

—IEEE 1076/1164 VHDL or IEEE 1364 Verilog context

sensitive editing

—Active-HDL FSM graphical finite state machine editor

—Active-HDL SIM post-synthesis timing simulator

—Architecture Explorer for detailed design analysis

—Static Timing Analyzer for critical path analysis

—Available on Windows

95/98/2000/XP and

Windows NT for $99

—Supports all Cypress programmable logic products

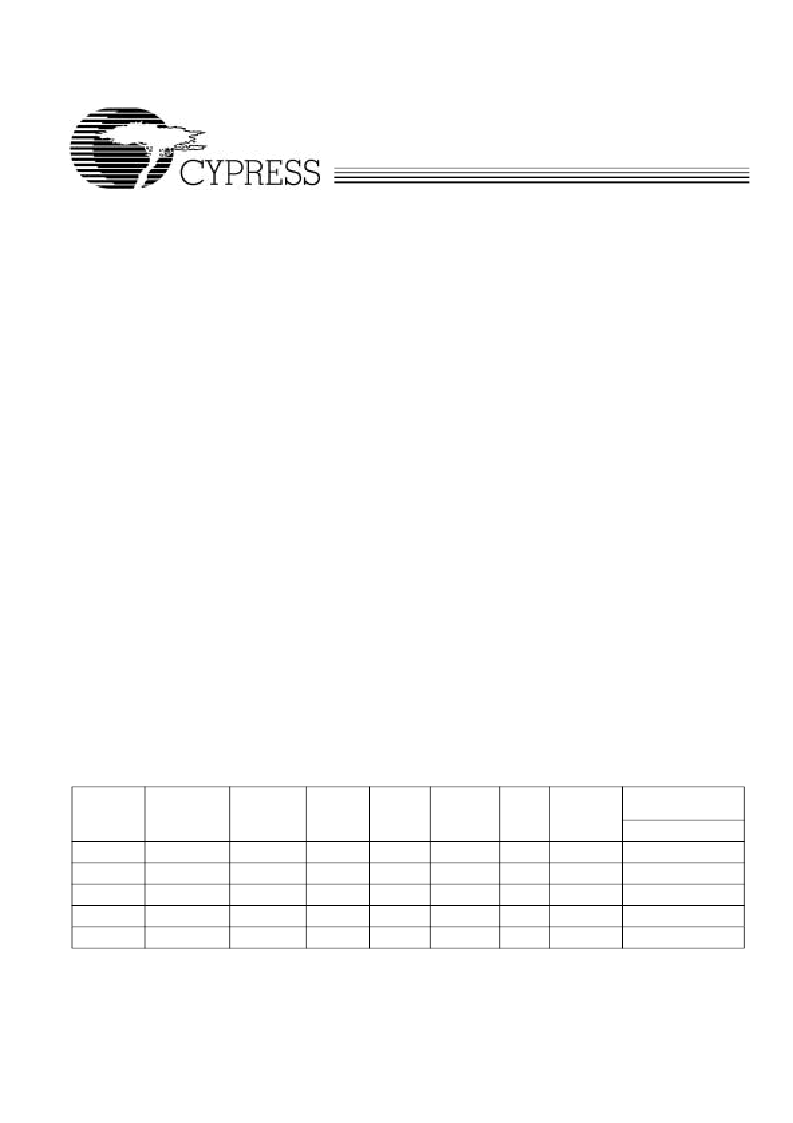

Delta39K ISR CPLD Family Members

Device

Typical

Gates

[1]

Macrocells

Cluster

memory

(Kbits)

Channel

memory

(Kbits)

Maximum

I/O Pins

f

(MHz)

Speed-t

Pin-to-Pin

(ns)

Standby I

CC

[2]

T

A

= 25

°

3.3/2.5V

39K30

16K – 48K

512

64

16

174

233

7.2

5 mA

39K50

23K – 72K

768

96

24

218

233

7.2

5 mA

39K100

46K – 144K

1536

192

48

302

222

7.5

10 mA

39K165

77K – 241K

2560

320

80

386

181

8.5

20 mA

39K200

92K – 288K

3072

384

96

428

181

8.5

20 mA

Notes:

1.

2.

Upper limit of typical gates is calculated by assuming only 10% of the channel memory is used.

Standby I

CC

values are with PLL not utilized, no output load and stable inputs.

相關PDF資料 |

PDF描述 |

|---|---|

| CY39100V388-125MBC | CPLDs at FPGA Densities |

| CY39100V388-125MBI | CPLDs at FPGA Densities |

| CY39165Z676-83MGC | CPLDs at FPGA Densities |

| CY39165Z676-83MGI | CPLDs at FPGA Densities |

| CY39165Z676-83NC | CPLDs at FPGA Densities |

相關代理商/技術參數 |

參數描述 |

|---|---|

| CY39100V388-125MGC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39100V388-181MBC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39100V388-181MGC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39100V388-181NC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39100V388-233MGC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

發布緊急采購,3分鐘左右您將得到回復。