- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄376711 > DG526AK883B (Intersil Corporation) Analog CMOS Latchable Multiplexers PDF資料下載

參數(shù)資料

| 型號(hào): | DG526AK883B |

| 廠商: | Intersil Corporation |

| 英文描述: | Analog CMOS Latchable Multiplexers |

| 中文描述: | 模擬CMOS鎖存多路復(fù)用器 |

| 文件頁(yè)數(shù): | 1/16頁(yè) |

| 文件大小: | 308K |

| 代理商: | DG526AK883B |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

12-1

Semiconductor

Features

Direct RESET

TTL and CMOS Compatible Address and Enable

Inputs

Maximum Power Supply Rating . . . . . . . . . . . . . . . .44V

Break-Before-Make Switching

Alternate Source

Applications

Data Acquisition Systems

Communication Systems

Automatic Test Equipment

Microprocessor Controlled Systemd

Description

The DG526, DG527, DG528, and DG529 are CMOS

Monolithic 16-Channel/Dual 4-Channel Analog Multiplexers.

Each device has on-chip address and control latches to sim-

plify design in microprocessor based applications. The DG526

uses 4 address lines to control its 16 channels; the DG527,

DG528 both use 3 address lines to control their 8 channels;

and the DG529 uses 2 address lines to control its 4 channels.

The enable pin is used to enable the address latches during

the WR pulse. It can be hard wired to the logic supply if one of

the channels will always be used (except during a reset) or it

can be tied to address decoding circuitry for memory mapped

operation. The RS pin is used to clear all latches regardless of

the state of any other latch or control line. The WR pin is used

to transfer the state of the address control lines to their

latches, except during a reset or when EN is low.

A channel in the ON state conducts signals equally well in

both directions. In the OFF state each channel blocks volt-

ages up to the supply rails. The address inputs, WR, RS and

the enable input are TTL and CMOS compatible over the full

specified operation temperature range.

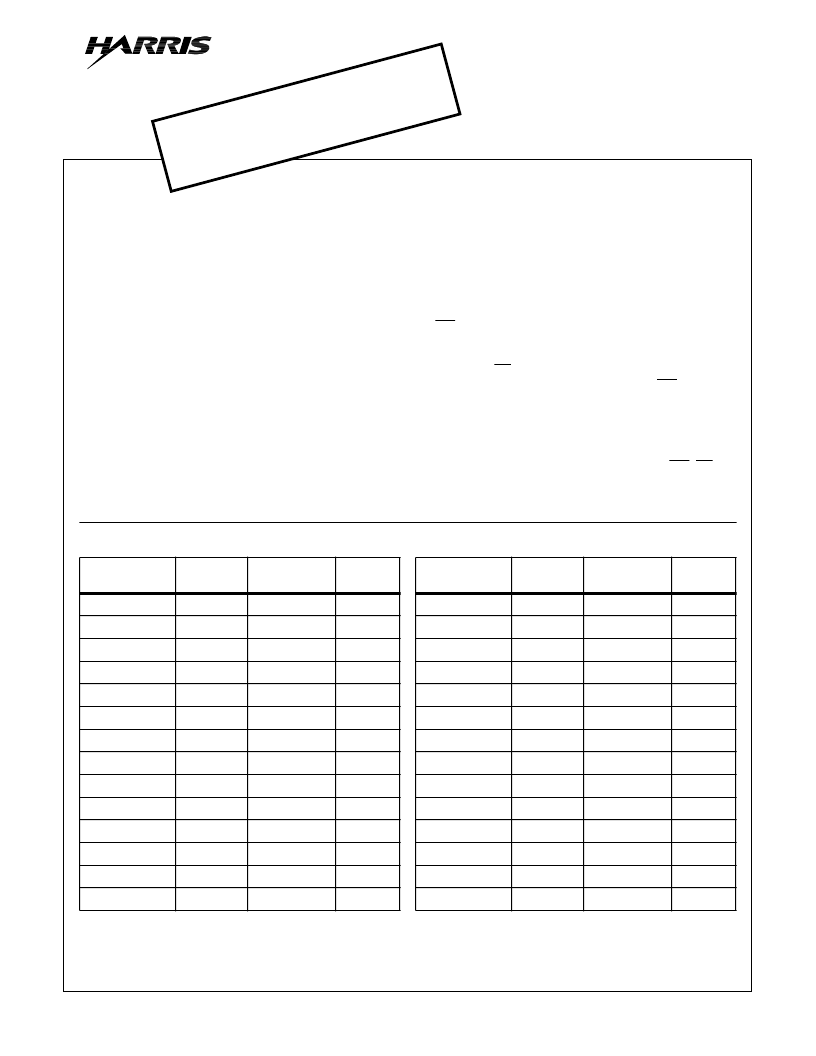

Part Number Information

PART

NUMBER

TEMP.

RANGE (

o

C)

PACKAGE

PKG. NO.

DG526AK

-55 to 125

28 Ld CERDIP

F28.6

DG526AK/883B

-55 to 125

28 Ld CERDIP

F28.6

DG526BK

-25 to 85

28 Ld CERDIP

F28.6

DG526BY

-25 to 85

28 Ld SOIC

M28.3

DG526CJ

0 to 70

28 Ld PDIP

E28.6

DG526CK

0 to 70

28 Ld CERDIP

F28.6

DG526CY

0 to 70

28 Ld SOIC

M28.3

DG527AK

-55 to 125

28 Ld CERDIP

F28.6

DG527AK/883B

-55 to 125

28 Ld CERDIP

F28.6

DG527BK

-25 to 85

28 Ld CERDIP

F28.6

DG527BY

-25 to 85

28 Ld SOIC

M28.3

DG527CJ

0 to 70

28 Ld PDIP

E28.6

DG527CK

0 to 70

28 Ld CERDIP

F28.6

DG527CY

0 to 70

28 Ld SOIC

M28.3

DG528AK

-55 to 125

18 Ld CERDIP

F18.3

DG528AK/883B

-55 to 125

18 Ld CERDIP

F18.3

DG528BK

-25 to 85

18 Ld CERDIP

F18.3

DG528BY

-25 to 85

18 Ld SOIC

M18.3

DG528CJ

0 to 70

18 Ld PDIP

E18.3

DG528CK

0 to 70

18 Ld CERDIP

F18.3

DG528CY

0 to 70

18 Ld SOIC

M18.3

DG529AK

-55 to 125

18 Ld CERDIP

F18.3

DG529AK/883B

-55 to 125

18 Ld CERDIP

F18.3

DG529BK

-25 to 85

18 Ld CERDIP

F18.3

DG529BY

-25 to 85

18 Ld SOIC

M18.3

DG529CJ

0 to 70

18 Ld PDIP

E18.3

DG529CK

0 to 70

18 Ld CERDIP

F18.3

DG529CY

0 to 70

18 Ld SOIC

M18.3

PART

NUMBER

TEMP.

RANGE (

o

C)

PACKAGE

PKG. NO.

April 1999

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

Harris Corporation 1999

DG526, DG527,

DG528, DG529

Analog CMOS

Latchable Multiplexers

File Number

3139.2

FOR A POSSIBLE SUBSTITUTE PRODUCT

call Central Applications 1-800-442-7747

or email: centapp@harris.com

OBSOLETE PRODUCT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DG528CWN | 8-Channel Latchable Multiplexers |

| DG529CWN | 8-Channel Latchable Multiplexers |

| DG528AK | 8-Channel Latchable Multiplexers |

| DG528AZ | 8-Channel Latchable Multiplexers |

| DG528CJ | 8-Channel Latchable Multiplexers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DG526BK | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Analog CMOS Latchable Multiplexers |

| DG526BY | 制造商:Harris Corporation 功能描述: |

| DG526BY WAF | 制造商:Harris Corporation 功能描述: |

| DG526CJ | 制造商:Rochester Electronics LLC 功能描述:28 PDIP 0+70 15.0V 16-CHANNEL LATCHABLE CMOS ANALOG MUX - Bulk |

| DG526CK | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。