- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376761 > DM2212J1-12L Enhanced DRAM (EDRAM) PDF資料下載

參數(shù)資料

| 型號: | DM2212J1-12L |

| 英文描述: | Enhanced DRAM (EDRAM) |

| 中文描述: | 增強的DRAM(eDRAM內(nèi)存) |

| 文件頁數(shù): | 1/19頁 |

| 文件大小: | 159K |

| 代理商: | DM2212J1-12L |

DM2202/2212 EDRAM

1Mbx 4 EnhancedDynamc RAM

ProductSpecifcaton

1996 Enhanced Memory Systems Inc.,

1850 Ramtron Drive, Colorado Springs, CO

Telephone

(800) 545-DRAM;

Fax

(719) 488-9095; http://wwwcsn.net/ramtron/enhanced

80921

38-2107-002

The information contained herein is subject to change wthout notice.

Enhanced reserves the right to change or discontinue this product wthout notice.

Features

I

2Kbit SRAMCache Memory for 12ns RandomReads Wthin a Page

I

Fast 4Mbit DRAMArray for 30ns Access to Any NewPage

I

Write Posting Register for 12ns RandomWrites and Burst Writes

Wthin a Page (Hit or Mss)

I

256-byte Wde DRAMto SRAMBus for 14.2 Ggabytes/Sec Cache

Fill

I

On-chip Cache Hit/Mss Comparators Maintain Cache Coherency

on Writes

I

Hidden Precharge and Refresh Cycles

I

Write-per-bit Option (DM2212) for Parity and Video Applications

I

Extended 64ms Refresh Period for LowStandby Power

I

300 Ml Plastic SOJ and TSOP-II Package Options

I

+5 and +3.3 Volt Power Supply Voltage Options

I

LowPower, Self Refresh Mode Option

I

Industrial Temperature Range Option

Description

The 4Mb Enhanced DRAM(EDRAM combines rawspeed wth

innovative architecture to offer the optimumcost-performance solution

for high performance local or systemmain memory In most high

speed applications, no-wait-state performance can be achieved wthout

secondary SRAMcache and wthout interleaving main memory banks at

systemclock speeds through 50MHz. Two-way interleave wll allowno-

wait-state operation at clock speeds greater than 100MHz wthout the

need of secondary SRAMcache. The EDRAMoutperforms conventional

SRAMcache plus DRAMmemory systems by mnimzing processor wait

states for all possible bus events, not just cache hits. The combination

of data and address latching, 2K of fast on-chip SRAMcache, and

simplified on-chip cache control allows systemlevel flexibility

performance, and overall memory cost reduction not available wth any

other high density memory component. Architectural simlarity wth

JEDEC DRAMs allows a single memory controller design to support

either slowJEDEC DRAMs or high speed EDRAMs. A systemdesigned in

this manner can provide a simple upgrade path to higher system

performance.

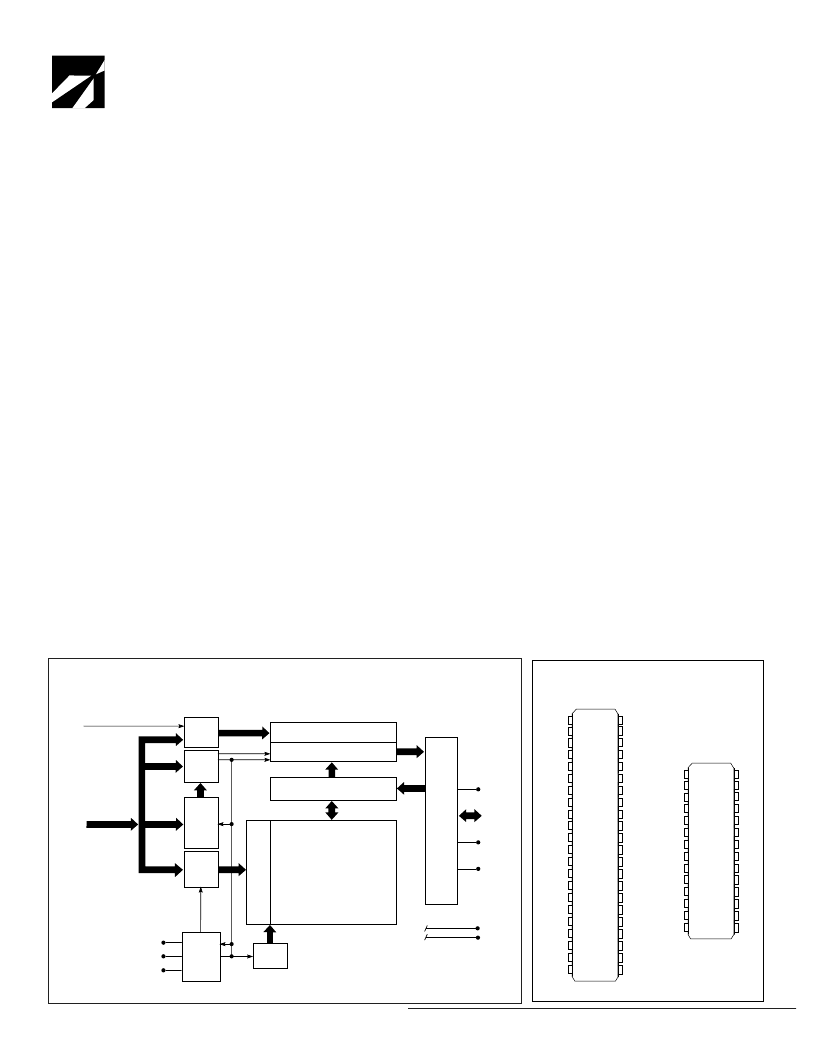

Archtecture

The EDRAMarchitecturehas a simple integrated SRAMcache

which allows it to operate much like a page mode or static column

DRAM

The EDRAMs SRAMcache is integrated into the DRAMarray as

tightly coupled rowregisters. Memory reads always occur fromthe

cache rowregister. When the internal comparator detects a page hit,

only the SRAMis accessed and data is available in 12ns fromcolumn

address. When a page read mss is detected, the newDRAMrowis

loaded into the cache and data is available at the output all wthin

30ns fromrowenable. Subsequent reads wthin the page (burst reads

or randomreads) can continue at 12ns cycle time. Since reads occur

fromthe SRAMcache, the DRAMprecharge can occur simultaneously

wthout degrading performance. The on-chip refresh counter wth

independent refresh bus allows the EDRAMto be refreshed during

cache reads.

Memory writes are internally posted in 12ns and directed to the

DRAMarray During a write hit, the on-chip address comparator

activates a parallel write path to the SRAMcache to maintain

/CAL

A

0-10

W/R

/F

/RE

V

V

Sense Amps

& Column Write Select

Column Decoder

Row

Add

Latch

CC

SS

512 X 4 Cache (Row Register)

Memory

Array

(2048 X 512 X 4)

A

0-8

/G

/S

/WE

DQ

0-3

Column

Add

Latch

11 Bit

Comp

Last

Row

Read

Add

Latch

I/O

Control

and

Data

Latches

Refresh

Counter

R

Row Add

and

Refresh

Control

A

0-9

Functional Dagram

SO Pin

Configuration

TSOP-II Pin

Configuration

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

V

SS *

V

SS

V

SS

DQ

0

DQ

1

DQ

2

NC

DQ

3

/G

V

CC

V

CC

V

SS

V

SS

/WE

/S

/F

NC

W/R

NC

/CAL

A

10

NC

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

NC

A

0

NC

A

1

NC

A

3

A

4

NC

A

5

/RE

V

CC

V

SS

V

SS

A

6

A

7

A

8

NC

A

2

NC

A

9

V

CC

V

CC*

* Reserved for future use

1

2

3

4

5

6

7

9

10

11

12

13

26

25

24

23

22

21

20

18

17

16

15

14

A

A

1

A

3

A

4

A

5

/RE

V

CC

V

SS

A

6

A

7

A

8

A

2

A

9

V

CC

8

19

27

28

0

V

SS

DQ

DQ

1

DQ

2

DQ

3

/WE

/S

/F

W/R

/CAL

A

10

/G

V

CC

V

SS

0

Enhanced

Memory Systems Inc.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM2212J1-15 | Enhanced DRAM (EDRAM) |

| DM2212J1-15I | Enhanced DRAM (EDRAM) |

| DM2212J1-15L | Enhanced DRAM (EDRAM) |

| DM2200J1-12 | Enhanced DRAM (EDRAM) |

| DM2200J1-12I | Enhanced DRAM (EDRAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM2212J1-15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

| DM2212J1-15I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

| DM2212J1-15L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

| DM2212J-12 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

| DM2212J-12I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。