- 您現在的位置:買賣IC網 > PDF目錄376781 > DM74ALS240A (Fairchild Semiconductor Corporation) Octal 3-STATE Bus Driver PDF資料下載

參數資料

| 型號: | DM74ALS240A |

| 廠商: | Fairchild Semiconductor Corporation |

| 英文描述: | Octal 3-STATE Bus Driver |

| 中文描述: | 八路三態總線驅動器 |

| 文件頁數: | 1/7頁 |

| 文件大小: | 78K |

| 代理商: | DM74ALS240A |

2000 Fairchild Semiconductor Corporation

DS006210

www.fairchildsemi.com

September 1986

Revised February 2000

D

DM74ALS240A DM74ALS241A

Octal 3-STATE Bus Driver

General Description

These octal 3-STATE bus drivers are designed to provide

the designer with flexibility in implementing a bus interface

with memory, microprocessor, or communication systems.

The output 3-STATE gating control is organized into two

separate groups of four buffers. The DM74ALS240A con-

trol inputs symmetrically enable the respective outputs

when set logic LOW, while the DM74ALS241A has comple-

mentary enable gating. The 3-STATE circuitry contains a

feature that maintains the buffer outputs in 3-STATE (high

impedance state) during power supply ramp-up or ramp-

down. This eliminates bus glitching problems that arise

during power-up and power-down.

Features

I

Advanced low power oxide-isolated ion-implanted

Schottky TTL process

I

Functional and pin compatible with the DM74LS coun-

terpart

I

Improved switching performance with less power dissi-

pation compared with the DM74LS counterpart

I

Switching response specified into 500

and 50 pF load

I

Switching response specifications guaranteed over full

temperature and V

CC

supply range

I

PNP input design reduces input loading

I

Low level drive current: 74ALS

=

24 mA

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

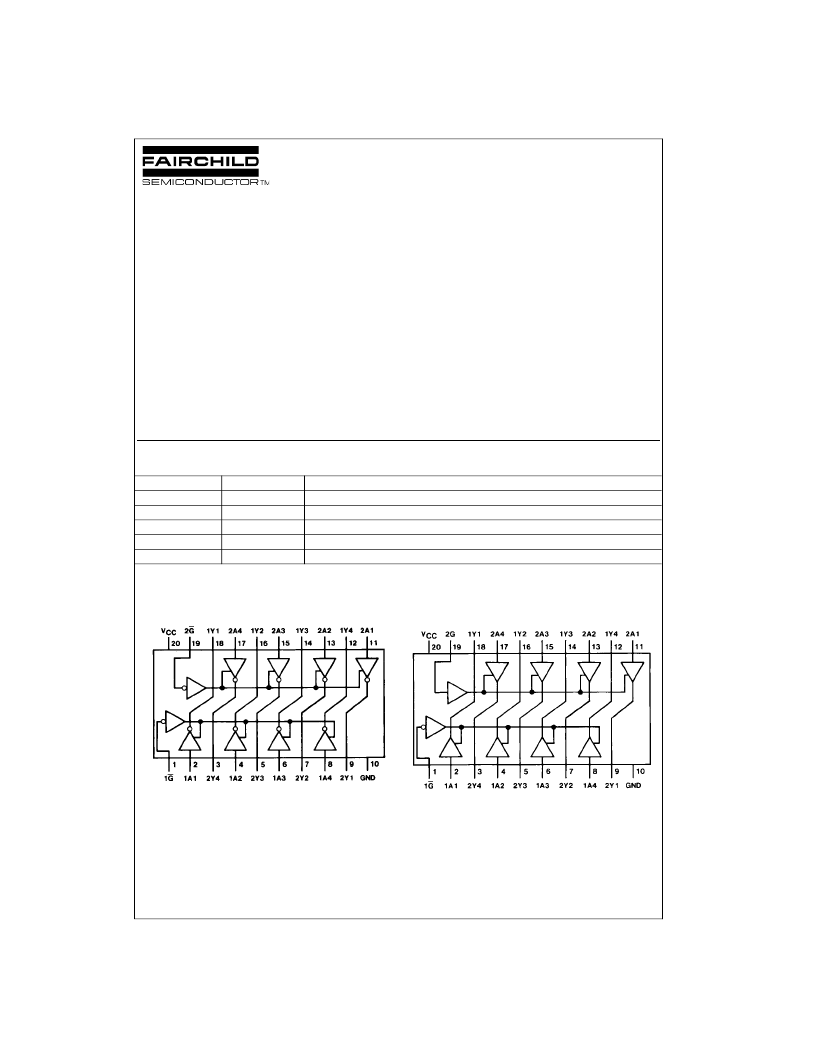

Connection Diagrams

DM74ALS240A

DM74ALS241A

Order Number

DM74ALS240AWM

DM74ALS240ASJ

DM74ALS240AN

DM74ALS241AWM

DM74ALS241AN

Package Number

M20B

M20D

N20A

M20B

N20A

Package Description

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

相關PDF資料 |

PDF描述 |

|---|---|

| DM74ALS240AN | Octal 3-STATE Bus Driver |

| DM74ALS240ASJ | Octal 3-STATE Bus Driver |

| DM74ALS241AN | Octal 3-STATE Bus Driver |

| DM74ALS241AWM | Octal 3-STATE Bus Driver |

| DM74ALS240ASJX | Dual 4-Bit Inverting Buffer/Driver |

相關代理商/技術參數 |

參數描述 |

|---|---|

| DM74ALS240A_07 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Octal 3-STATE Bus Driver |

| DM74ALS240A-1N | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Dual 4-Bit Inverting Buffer/Driver |

| DM74ALS240A-1WM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Dual 4-Bit Inverting Buffer/Driver |

| DM74ALS240AJ/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Dual 4-Bit Inverting Buffer/Driver |

| DM74ALS240AJ-1/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Dual 4-Bit Inverting Buffer/Driver |

發布緊急采購,3分鐘左右您將得到回復。