- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376787 > DM74LS112AN (FAIRCHILD SEMICONDUCTOR CORP) Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop with Preset, Clear, and Complementary Outputs PDF資料下載

參數(shù)資料

| 型號(hào): | DM74LS112AN |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop with Preset, Clear, and Complementary Outputs |

| 中文描述: | LS SERIES, DUAL NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, PDIP16 |

| 封裝: | 0.300 INCH, PLASTIC, MS-001, DIP-16 |

| 文件頁數(shù): | 1/5頁 |

| 文件大小: | 52K |

| 代理商: | DM74LS112AN |

2000 Fairchild Semiconductor Corporation

DS006382

www.fairchildsemi.com

August 1986

Revised March 2000

D

O

DM74LS112A

Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop

with Preset, Clear, and Complementary Outputs

General Description

This device contains two independent negative-edge-trig-

gered J-K flip-flops with complementary outputs. The J and

K data is processed by the flip-flop on the falling edge of

the clock pulse. The clock triggering occurs at a voltage

level and is not directly related to the transition time of the

falling edge of the clock pulse. Data on the J and K inputs

may be changed while the clock is HIGH or LOW without

affecting the outputs as long as the setup and hold times

are not violated. A low logic level on the preset or clear

inputs will set or reset the outputs regardless of the logic

levels of the other inputs.

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

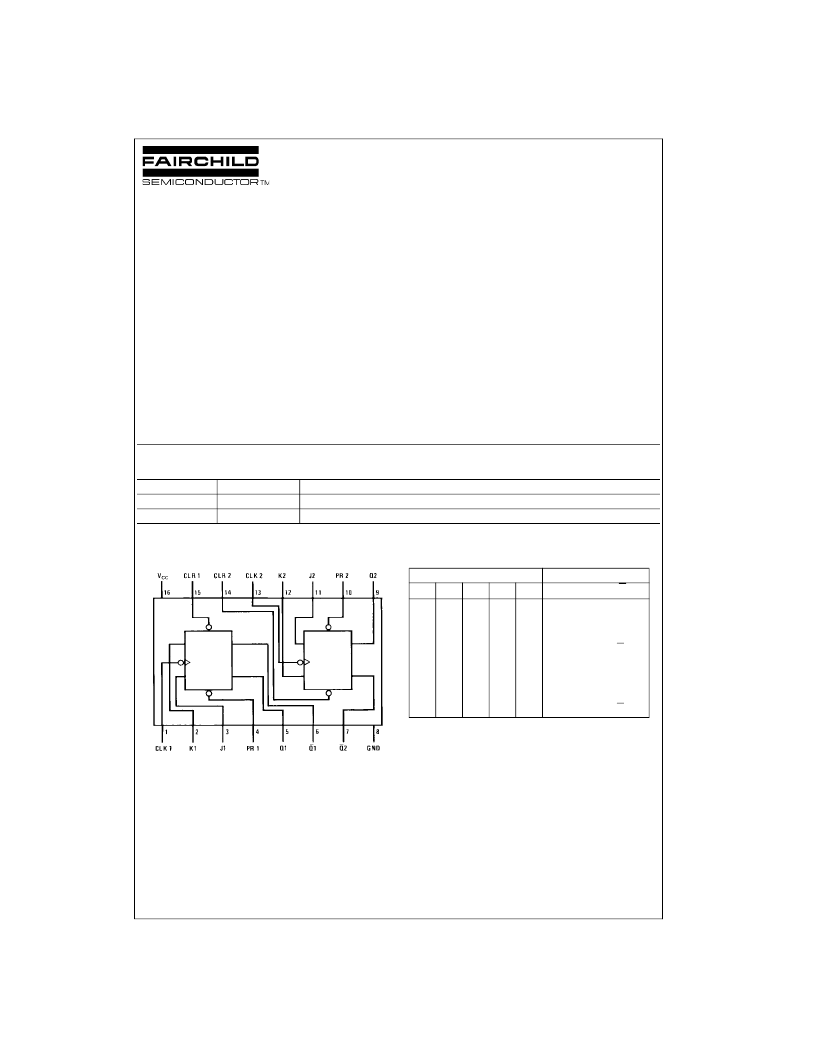

Connection Diagram

Function Table

H

=

HIGH Logic Level

L

=

LOW Logic Level

X

=

Either LOW or HIGH Logic Level

↓

=

Negative Going Edge of Pulse

Q

0

=

The output logic level before the indicated input conditions were

established.

Toggle

=

Each output changes to the complement of its previous level on

each falling edge of the clock pulse.

Note 1:

This configuration is nonstable; that is, it will not persist when

preset and/or clear inputs return to their inactive (HIGH) level.

Order Number

DM74KS112AM

DM74LS112AN

Package Number

M16A

N16E

Package Description

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Inputs

Outputs

PR

L

H

L

H

H

H

H

CLR CLK

H

L

L

H

H

H

H

J

X

X

X

L

H

L

H

K

X

X

X

L

L

H

H

Q

H

L

Q

L

H

X

X

X

↓

↓

↓

↓

H

H (Note 1)

Q

0

H

L

H (Note 1)

Q

0

L

H

Toggle

H

H

X

X

Q

0

Q

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM74LS11M | Triple 3-Input AND Gate |

| DM74LS11 | Triple 3-Input AND Gate(三3輸入與門) |

| DM74LS11N | Triple 3-Input AND Gate |

| DM74LS11MX | Triple 3-input AND Gate |

| DM74LS123SJ | Dual Retriggerable One-Shot with Clear and Complementary Outputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM74LS11M | 功能描述:邏輯門 Trp 3-Input AND Gate RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時(shí)間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| DM74LS11MX | 功能描述:邏輯門 Trp 3-Input AND Gate RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時(shí)間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| DM74LS11N | 功能描述:邏輯門 Trp 3-Input AND Gate RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時(shí)間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| DM74LS11NNSC84 | 制造商:National Semiconductor 功能描述:74LS11N NSC'88 |

| DM74LS122N | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。