- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄22012 > EP1K100FC256-2N (Altera)IC ACEX 1K FPGA 100K 256-FBGA PDF資料下載

參數(shù)資料

| 型號: | EP1K100FC256-2N |

| 廠商: | Altera |

| 文件頁數(shù): | 31/86頁 |

| 文件大小: | 0K |

| 描述: | IC ACEX 1K FPGA 100K 256-FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | ACEX-1K® |

| LAB/CLB數(shù): | 624 |

| 邏輯元件/單元數(shù): | 4992 |

| RAM 位總計(jì): | 49152 |

| 輸入/輸出數(shù): | 186 |

| 門數(shù): | 257000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 256-BGA |

| 供應(yīng)商設(shè)備封裝: | 256-FBGA(17x17) |

| 其它名稱: | 544-1820 EP1K100FC256-2N-ND |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁

Altera Corporation

37

ACEX 1K Programmable Logic Device Family Data Sheet

D

e

ve

lo

pm

e

n

t

13

To

o

ls

For designs that require both a multiplied and non-multiplied clock, the

clock trace on the board can be connected to the GCLK1 pin. In the Altera

software, the GCLK1 pin can feed both the ClockLock and ClockBoost

circuitry in the ACEX 1K device. However, when both circuits are used,

the other clock pin cannot be used.

ClockLock & ClockBoost Timing Parameters

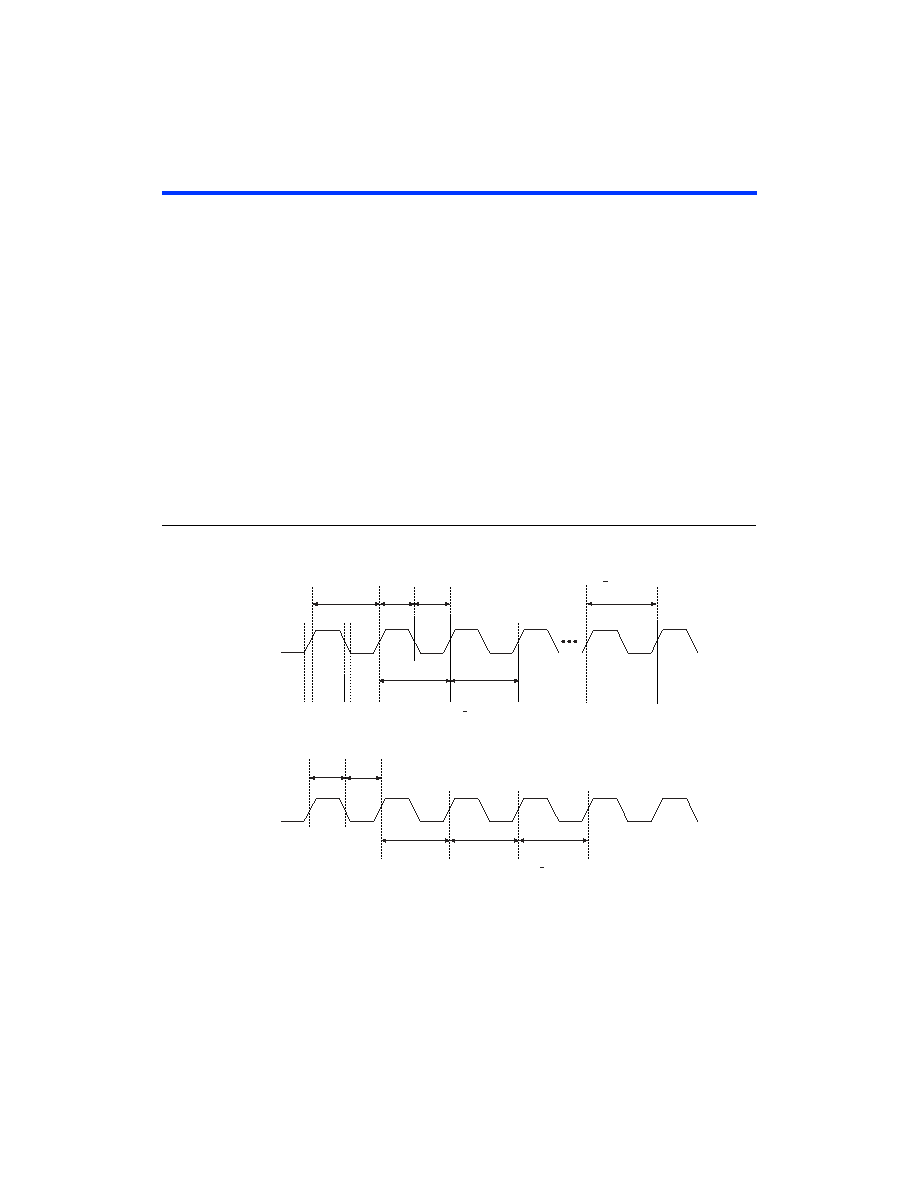

For the ClockLock and ClockBoost circuitry to function properly, the

incoming clock must meet certain requirements. If these specifications are

not met, the circuitry may not lock onto the incoming clock, which

generates an erroneous clock within the device. The clock generated by

the ClockLock and ClockBoost circuitry must also meet certain

specifications. If the incoming clock meets these requirements during

configuration, the ClockLock and ClockBoost circuitry will lock onto the

clock during configuration. The circuit will be ready for use immediately

after configuration. Figure 19 shows the incoming and generated clock

specifications.

Figure 19. Specifications for the Incoming & Generated Clocks

Note:

(1)

The tI parameter refers to the nominal input clock period; the tO parameter refers to the nominal output clock

period.

Input

Clock

ClockLock

Generated

Clock

tCLK1

tINDUTY

tI+ tCLKDEV

tR

tF

tO

tI+ tINCLKSTB

tO

tO tJITTER

tO+ tJITTER

tOUTDUTY

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VI-BNJ-CW | CONVERTER MOD DC/DC 36V 100W |

| TAP686M010CRW | CAP TANT 68UF 10V 20% RADIAL |

| EP1K100FC484-3N | IC ACEX 1K FPGA 100K 484-FBGA |

| TAP686M010BRW | CAP TANT 68UF 10V 20% RADIAL |

| EPF10K30ETC144-3 | IC FLEX 10KE FPGA 30K 144-TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP1K100FC2563 | 制造商:Altera Corporation 功能描述: |

| EP1K100FC256-3 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - ACEX 1K 624 LABs 186 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1K100FC256-3N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - ACEX 1K 624 LABs 186 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1K100FC484-1 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - ACEX 1K 624 LABs 333 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1K100FC484-1N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - ACEX 1K 624 LABs 333 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。