- 您現在的位置:買賣IC網 > PDF目錄97926 > EPF10K100B Programmable Logic PDF資料下載

參數資料

| 型號: | EPF10K100B |

| 英文描述: | Programmable Logic |

| 中文描述: | 可編程邏輯 |

| 文件頁數: | 1/138頁 |

| 文件大小: | 2116K |

| 代理商: | EPF10K100B |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁

Altera Corporation

1

FLEX 10K

Embedded

Programmable Logic Family

June 1999, ver. 4.01

Data Sheet

A-DS-F10K-04.01

Includes

FLEX 10KA

Features...

s

The industry’s first embedded programmable logic device (PLD)

family, providing System-on-a-Programmable-ChipTM integration

–

Embedded array for implementing megafunctions, such as

efficient memory and specialized logic functions

–

Logic array for general logic functions

s

High density

–

–

Up to 40,960 RAM bits; 2,048 bits per embedded array block

(EAB), all of which can be used without reducing logic capacity

s

System-level features

–

MultiVoltTM I/O interface support

–

5.0-V tolerant input pins in FLEX 10KA devices

–

Low power consumption (typical specification less than 0.5 mA

in standby mode for most devices)

–

FLEX 10K and FLEX 10KA devices support peripheral

component interconnect Special Interest Group (PCI SIG) PCI

Local Bus Specification, Revision 2.2

–

FLEX 10KA devices include pull-up clamping diode, selectable

on a pin-by-pin basis for 3.3-V PCI compliance

–

Select FLEX 10KA devices support 5.0-V PCI buses with eight or

fewer loads

–

Built-in Joint Test Action Group (JTAG) boundary-scan test

(BST) circuitry compliant with IEEE Std. 1149.1-1990, available

without consuming any device logic

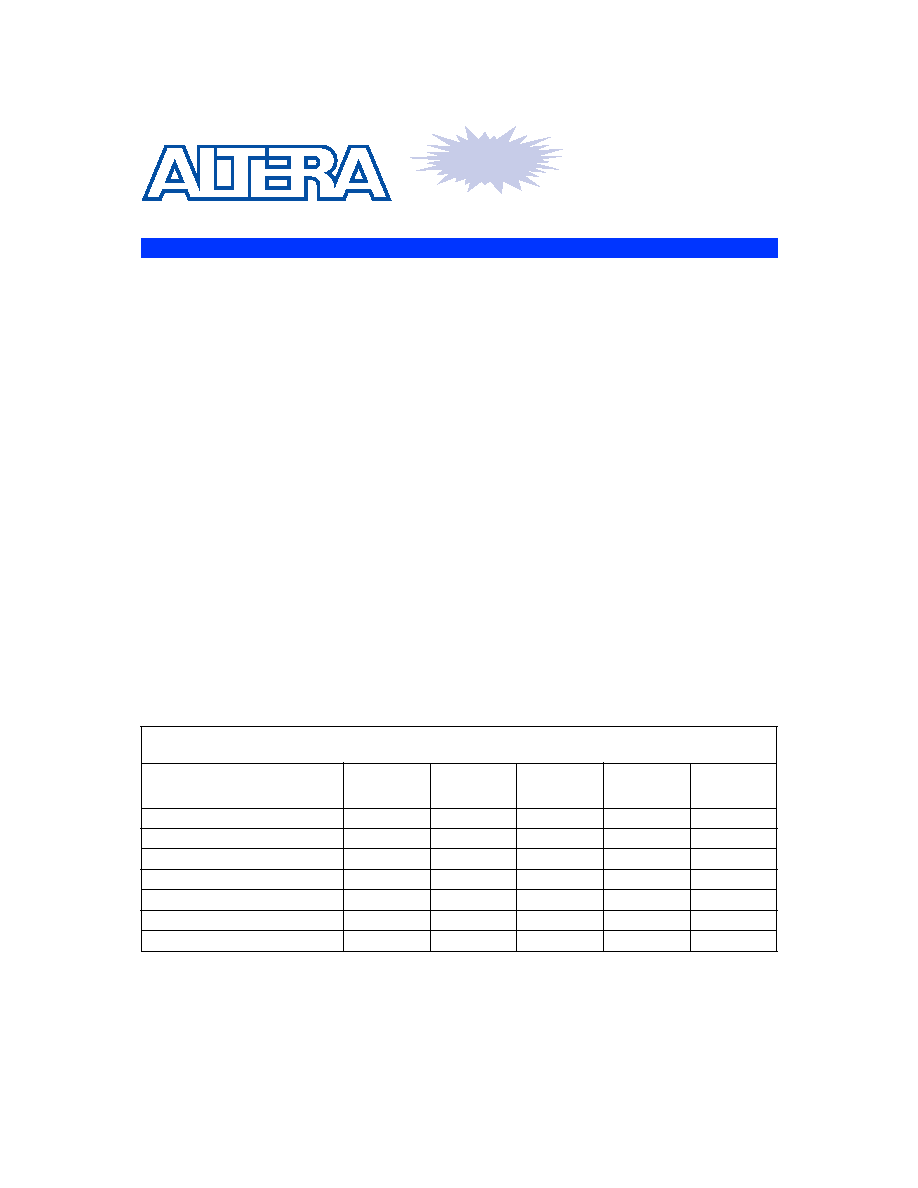

Table 1. FLEX 10K Device Features

Feature

EPF10K10

EPF10K10A

EPF10K20

EPF10K30

EPF10K30A

EPF10K40

EPF10K50

EPF10K50V

Typical gates (logic and RAM)

10,000

20,000

30,000

40,000

50,000

Maximum system gates

31,000

63,000

69,000

93,000

116,000

Logic elements (LEs)

576

1,152

1,728

2,304

2,880

Logic array blocks (LABs)

72

144

216

288

360

Embedded array blocks (EABs)

3668

10

Total RAM bits

6,144

12,288

16,384

20,480

Maximum user I/O pins

150

189

246

189

310

相關PDF資料 |

PDF描述 |

|---|---|

| EPF10K200S | Programmable Logic |

| EPF10K130EFC484-3 | Field Programmable Gate Array (FPGA) |

| EPF10K130EFC672-1 | Field Programmable Gate Array (FPGA) |

| EPF10K130EFC672-1X | Field Programmable Gate Array (FPGA) |

| EPF10K130EFC672-2 | Field Programmable Gate Array (FPGA) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| EPF10K100BFC256-1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EPF10K100BFC256-1DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EPF10K100BFC256-2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EPF10K100BFC256-2DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EPF10K100BFC256-3DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

發布緊急采購,3分鐘左右您將得到回復。