- 您現在的位置:買賣IC網 > PDF目錄22151 > EPM3032ALC44-4 (Altera)IC MAX 3000A CPLD 32 44-PLCC PDF資料下載

參數資料

| 型號: | EPM3032ALC44-4 |

| 廠商: | Altera |

| 文件頁數: | 1/46頁 |

| 文件大小: | 0K |

| 描述: | IC MAX 3000A CPLD 32 44-PLCC |

| 標準包裝: | 390 |

| 系列: | MAX® 3000A |

| 可編程類型: | 系統內可編程 |

| 最大延遲時間 tpd(1): | 4.5ns |

| 電壓電源 - 內部: | 3 V ~ 3.6 V |

| 邏輯元件/邏輯塊數目: | 2 |

| 宏單元數: | 32 |

| 門數: | 600 |

| 輸入/輸出數: | 34 |

| 工作溫度: | 0°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 44-LCC(J 形引線) |

| 供應商設備封裝: | 44-PLCC(16.58x16.58) |

| 包裝: | 管件 |

| 產品目錄頁面: | 603 (CN2011-ZH PDF) |

| 其它名稱: | 544-1967 EPM3032ALC44-4-ND |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

Altera Corporation

1

MAX 3000A

Programmable Logic

Device Family

June 2006, ver. 3.5

Data Sheet

DS-MAX3000A-3.5

Features...

■

High–performance, low–cost CMOS EEPROM–based programmable

■

3.3-V in-system programmability (ISP) through the built–in

IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface with

advanced pin-locking capability

–

ISP circuitry compliant with IEEE Std. 1532

■

Built–in boundary-scan test (BST) circuitry compliant with

IEEE Std. 1149.1-1990

■

Enhanced ISP features:

–

Enhanced ISP algorithm for faster programming

–

ISP_Done bit to ensure complete programming

–

Pull-up resistor on I/O pins during in–system programming

■

High–density PLDs ranging from 600 to 10,000 usable gates

■

4.5–ns pin–to–pin logic delays with counter frequencies of up to

227.3 MHz

■

MultiVoltTM I/O interface enabling the device core to run at 3.3 V,

while I/O pins are compatible with 5.0–V, 3.3–V, and 2.5–V logic

levels

■

Pin counts ranging from 44 to 256 in a variety of thin quad flat pack

(TQFP), plastic quad flat pack (PQFP), plastic J–lead chip carrier

(PLCC), and FineLine BGATM packages

■

Hot–socketing support

■

Programmable interconnect array (PIA) continuous routing structure

for fast, predictable performance

■

Industrial temperature range

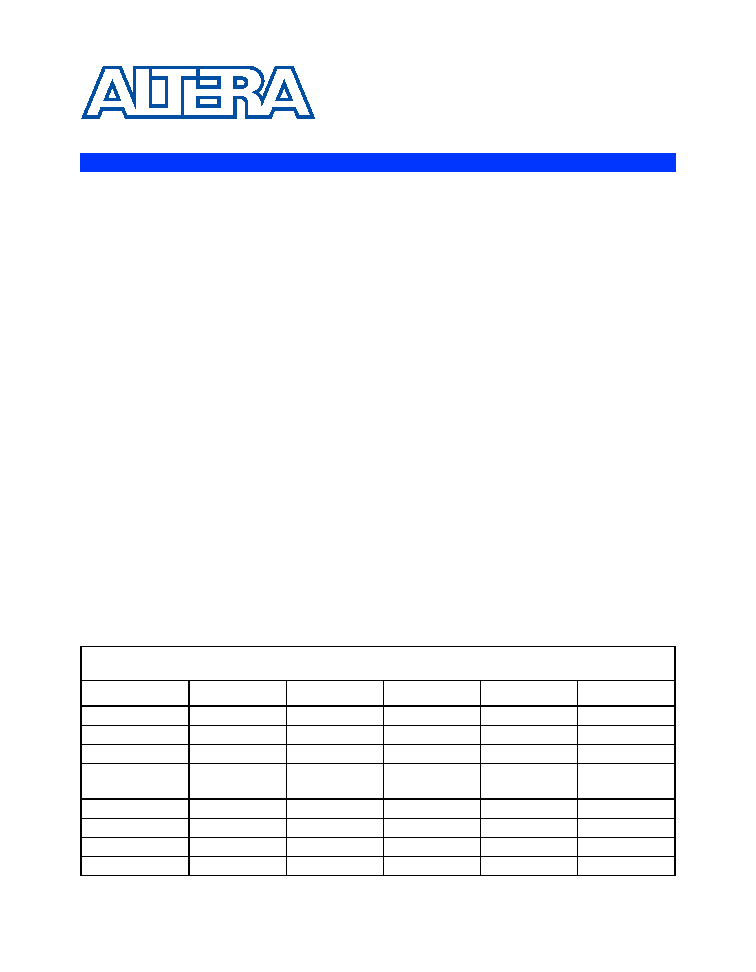

Table 1. MAX 3000A Device Features

Feature

EPM3032A

EPM3064A

EPM3128A

EPM3256A

EPM3512A

Usable gates

600

1,250

2,500

5,000

10,000

Macrocells

32

64

128

256

512

Logic array blocks

2

4

8

16

32

Maximum user I/O

pins

34

66

98

161

208

tPD (ns)

4.5

5.0

7.5

tSU (ns)

2.9

2.8

3.3

5.2

5.6

tCO1 (ns)

3.0

3.1

3.4

4.8

4.7

fCNT (MHz)

227.3

222.2

192.3

126.6

116.3

相關PDF資料 |

PDF描述 |

|---|---|

| VE-BWP-CY-F2 | CONVERTER MOD DC/DC 13.8V 50W |

| GEM18DTMN-S189 | CONN EDGECARD 36POS R/A .156 SLD |

| VE-JWP-CW-B1 | CONVERTER MOD DC/DC 13.8V 100W |

| VE-BWN-CY-F4 | CONVERTER MOD DC/DC 18.5V 50W |

| VE-BWN-CY-F3 | CONVERTER MOD DC/DC 18.5V 50W |

相關代理商/技術參數 |

參數描述 |

|---|---|

| EPM3032ALC44-4N | 功能描述:CPLD - 復雜可編程邏輯器件 CPLD - MAX 3000A 32 Macro 34 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3032ALC44-7 | 功能描述:CPLD - 復雜可編程邏輯器件 CPLD - MAX 3000A 32 Macro 34 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3032ALC44-7N | 功能描述:CPLD - 復雜可編程邏輯器件 CPLD - MAX 3000A 32 Macro 34 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3032ALI44-10 | 功能描述:IC MAX 3000A CPLD 32 44-PLCC RoHS:否 類別:集成電路 (IC) >> 嵌入式 - CPLD(復雜可編程邏輯器件) 系列:MAX® 3000A 標準包裝:24 系列:CoolRunner II 可編程類型:系統內可編程 最大延遲時間 tpd(1):7.1ns 電壓電源 - 內部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數目:24 宏單元數:384 門數:9000 輸入/輸出數:173 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:208-BFQFP 供應商設備封裝:208-PQFP(28x28) 包裝:托盤 |

| EPM3032ALI44-10N | 功能描述:CPLD - 復雜可編程邏輯器件 CPLD - MAX 3000A 32 Macro 34 IOs RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發布緊急采購,3分鐘左右您將得到回復。