- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375849 > FM3216-G (Electronic Theatre Controls, Inc.) Integrated Processor Companion with Memory PDF資料下載

參數(shù)資料

| 型號(hào): | FM3216-G |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Integrated Processor Companion with Memory |

| 中文描述: | 綜合處理器與記憶體伴侶 |

| 文件頁(yè)數(shù): | 11/20頁(yè) |

| 文件大小: | 285K |

| 代理商: | FM3216-G |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

Two-wire Interface

The FM32xx employs an industry standard two-wire

bus that is familiar to many users. This product is

unique since it incorporates two logical devices in

one chip. Each logical device can be accessed

individually. Although monolithic, it appears to the

system software to be two separate products. One is

a memory device. It has a Slave Address (Slave ID =

1010b) that operates the same as a stand-alone

memory device. The second device is a real-time

clock and processor companion which have a unique

Slave Address (Slave ID = 1101b).

FM3204/16/64/256

Rev 2.1

Dec. 2004

Page 11 of 20

By convention, any device that is sending data onto

the bus is the transmitter while the target device for

this data is the receiver. The device that is

controlling the bus is the master. The master is

responsible for generating the clock signal for all

operations. Any device on the bus that is being

controlled is a slave. The FM32xx is always a slave

device.

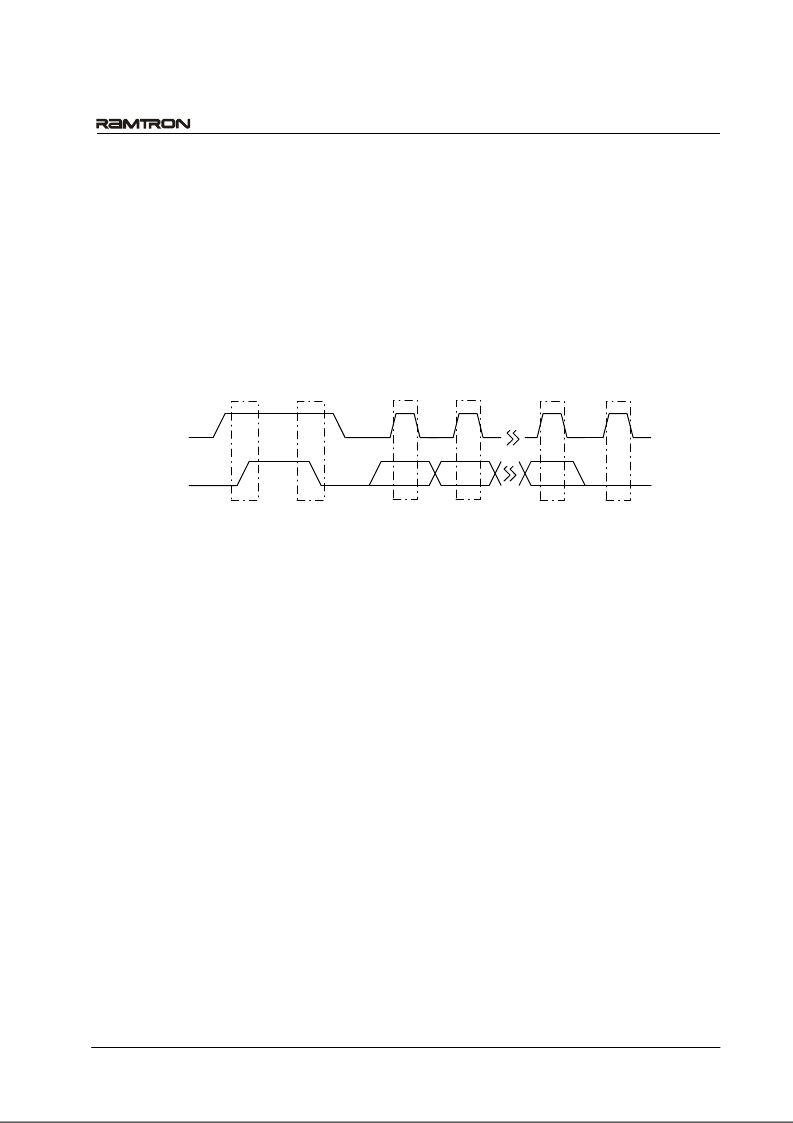

The bus protocol is controlled by transition states in

the SDA and SCL signals. There are four conditions:

Start, Stop, Data bit, and Acknowledge. The figure

below illustrates the signal conditions that specify

the four states. Detailed timing diagrams are shown

in the Electrical Specifications section.

Stop

(Master)

Start

(Master)

7

Data bits

(Transmitter)

6

0

Data bit

(Transmitter)

Acknowledge

(Receiver)

SCL

SDA

Figure 7. Data Transfer Protocol

Start Condition

A Start condition is indicated when the bus master

drives SDA from high to low while the SCL signal is

high. All read and write transactions begin with a

Start condition. An operation in progress can be

aborted by asserting a Start condition at any time.

Aborting an operation using the Start condition will

ready the FM32xx for a new operation.

If the power supply drops below the specified V

TP

during operation, any 2-wire transaction in progress

will be aborted and the system must issue a Start

condition prior to performing another operation.

Stop Condition

A Stop condition is indicated when the bus master

drives SDA from low to high while the SCL signal is

high. All operations must end with a Stop condition.

If an operation is pending when a stop is asserted,

the operation will be aborted. The master must have

control of SDA (not a memory read) in order to

assert a Stop condition.

Data/Address Transfer

All data transfers (including addresses) take place

while the SCL signal is high. Except under the two

conditions described above, the SDA signal should

not change while SCL is high.

Acknowledge

The Acknowledge (ACK) takes place after the 8

th

data bit has been transferred in any transaction.

During this state the transmitter must release the

SDA bus to allow the receiver to drive it. The

receiver drives the SDA signal low to acknowledge

receipt of the byte. If the receiver does not drive

SDA low, the condition is a No-Acknowledge

(NACK) and the operation is aborted.

The receiver might NACK for two distinct reasons.

First is that a byte transfer fails. In this case, the

NACK ends the current operation so that the part can

be addressed again. This allows the last byte to be

recovered in the event of a communication error.

Second and most common, the receiver does not

send an ACK to deliberately terminate an operation.

For example, during a read operation, the FM32xx

will continue to place data onto the bus as long as the

receiver sends ACKs (and clocks). When a read

operation is complete and no more data is needed,

the receiver must NACK the last byte. If the receiver

ACKs the last byte, this will cause the FM32xx to

attempt to drive the bus on the next clock while the

master is sending a new command such as a Stop.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FM3216-S | Integrated Processor Companion with Memory |

| FM32256 | Integrated Processor Companion with Memory |

| FM32256-G | Integrated Processor Companion with Memory |

| FM32256-S | Integrated Processor Companion with Memory |

| FM3264 | Integrated Processor Companion with Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FM3216-GTR | 功能描述:監(jiān)控電路 16K w/Pwr Mon WDT Bat Sw Pwr Fail RoHS:否 制造商:STMicroelectronics 監(jiān)測(cè)電壓數(shù): 監(jiān)測(cè)電壓: 欠電壓閾值: 過(guò)電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| FM3216-S | 功能描述:監(jiān)控電路 16K w/Pwr Mon WDT Bat Sw Pwr Fail RoHS:否 制造商:STMicroelectronics 監(jiān)測(cè)電壓數(shù): 監(jiān)測(cè)電壓: 欠電壓閾值: 過(guò)電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| FM3216-STR | 功能描述:監(jiān)控電路 16K w/Pwr Mon WDT Bat Sw Pwr Fail RoHS:否 制造商:STMicroelectronics 監(jiān)測(cè)電壓數(shù): 監(jiān)測(cè)電壓: 欠電壓閾值: 過(guò)電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| FM3222-0 | 制造商:Power-One 功能描述:DC/DC,SNGL-OUT - Bulk |

| FM32256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Integrated Processor Companion with Memory |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。