- 您現在的位置:買賣IC網 > PDF目錄375853 > FM8P56 (Electronic Theatre Controls, Inc.) EPROM/ROM-Based 8-Bit Microcontroller Series PDF資料下載

參數資料

| 型號: | FM8P56 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | EPROM/ROM-Based 8-Bit Microcontroller Series |

| 中文描述: | 存儲器/基于ROM的8位微控制器系列 |

| 文件頁數: | 18/50頁 |

| 文件大小: | 368K |

| 代理商: | FM8P56 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

FM8P54/56

Rev1.21 May 31, 2005

P.18/FM8P54/56

FEELING

TECHNOLOGY

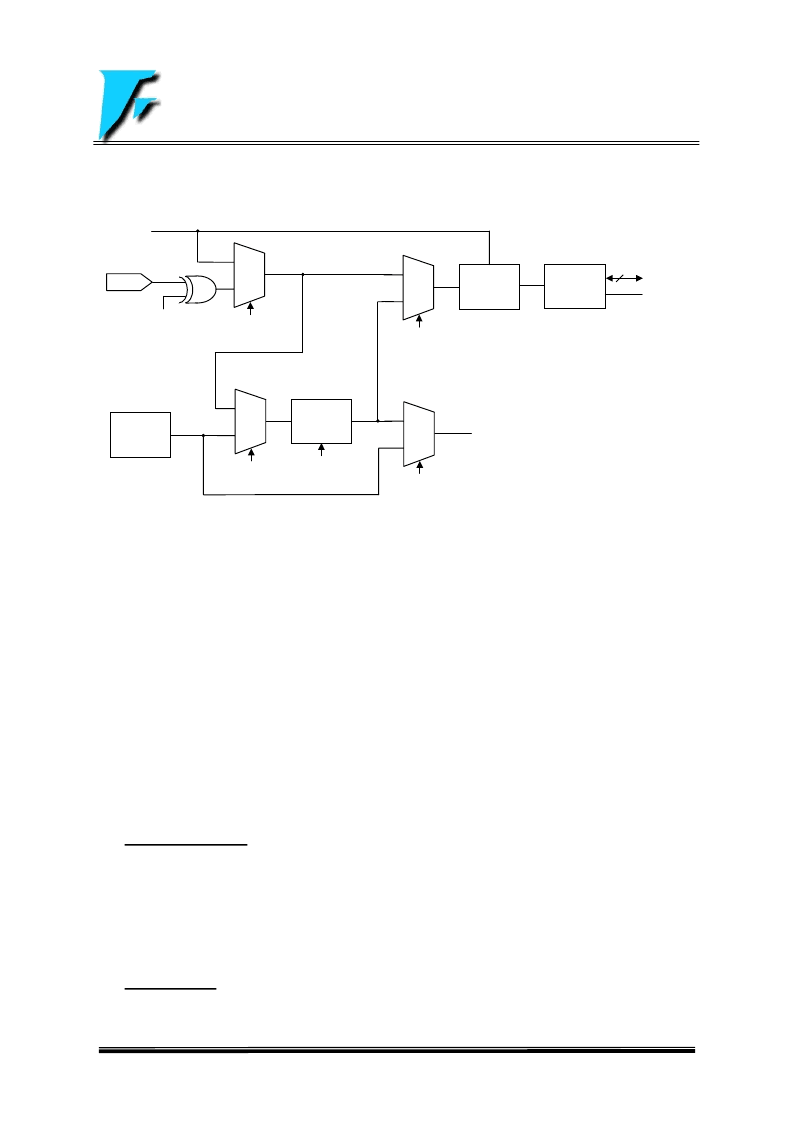

FIGURE 2.4: Block Diagram of The Timer0/WDT Prescaler

Instruction Cycle

(Fosc/4 or Fosc/2 or Fosc/8)

2.4 Interrupts

The FM8P54/56 series has up to three sources of interrupt:

1. External interrupt INT pin.

2. TMR0 overflow interrupt.

3. Port B input change interrupt (pins IOB7:IOB0).

INTFLAG is the interrupt flag register that recodes the interrupt requests in the relative flags.

A global interrupt enable bit, GIE (INTEN<7>), enables (if set) all un-masked interrupts or disables (if cleared) all

interrupts. Individual interrupts can be enabled/disabled through their corresponding enable bits in INTEN register

regardless of the status of the GIE bit.

When an interrupt event occur with the GIE bit and its corresponding interrupt enable bit are all set, the GIE bit will

be cleared by hardware to disable any further interrupts, and the next instruction will be fetched from address 008h.

The interrupt flag bits must be cleared by software before re-enabling GIE bit to avoid recursive interrupts.

The RETFIE instruction exits the interrupt routine and set the GIE bit to re-enable interrupt.

The flag bit (except PBIF bit) in INTFLAG register is set by interrupt event regardless of the status of its mask bit.

Reading the INTFLAG register will be the logic AND of INTFLAG and INTEN.

When an interrupt is generated by the INT instruction, the next instruction will be fetched from address 002h.

2.4.1 External INT Interrupt

External interrupt on INT pin is rising or falling edge triggered selected by INTEDG (OPTION<6>).

When a valid edge appears on the INT pin the flag bit INTIF (INTFLAG<2>) is set. This interrupt can be disabled by

clearing INTIE bit (INTEN<2>).

The INT pin interrupt can wake-up the system from SLEEP condition, if bit INTIE was set before going to SLEEP. If

GIE bit was set, the program will execute interrupt service routine after wake-up; or if GIE bit was cleared, the

program will execute next PC after wake-up.

2.4.2 Timer0 Interrupt

An overflow (FFh

00h) in the TMR0 register will set the flag bit T0IF (INTFLAG<0>). This interrupt can be

disabled by clearing T0IE bit (INTEN<0>).

T0CKI

T0SE

T0CS

MUX

0

1

MUX

0

1

Watchdog

Timer

PSA

8-Bit

Prescaler

PS2:PS0

WDT Time-out

MUX

1

0

PSA

MUX

1

0

PSA

Sync

2 Cycles

TMR0

Register

Data Bus

8

Set T0IF flag

on overflow

相關PDF資料 |

PDF描述 |

|---|---|

| FM8P56E | EPROM/ROM-Based 8-Bit Microcontroller Series |

| FM93C06 | 256-Bit Serial CMOS EEPROM(256位的串行CMOS EEPROM) |

| FM93C06E | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| FM93C06V | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| FM93C06EM8 | Microwire Serial EEPROM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| FM8P56E | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EPROM/ROM-Based 8-Bit Microcontroller Series |

| FM8PE53-SOP14 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:臺灣原裝進口,質量保證,免費燒錄,15014096573袁生 |

| FM8PE53-SOP8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:原裝現貨,量多從優,質量保證,15014096573/QQ407538145 |

| FM8PS53-SOP14 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:當天出貨,質量保證15014096573 |

| FM8PS53-SOP8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:大量現貨,免費燒錄,15014096573,袁小姐 |

發布緊急采購,3分鐘左右您將得到回復。