- 您現在的位置:買賣IC網 > PDF目錄370305 > GAL22V10-25LPI Electrically-Erasable PLD PDF資料下載

參數資料

| 型號: | GAL22V10-25LPI |

| 英文描述: | Electrically-Erasable PLD |

| 中文描述: | 電可擦除可編程邏輯器件 |

| 文件頁數: | 1/18頁 |

| 文件大小: | 223K |

| 代理商: | GAL22V10-25LPI |

1

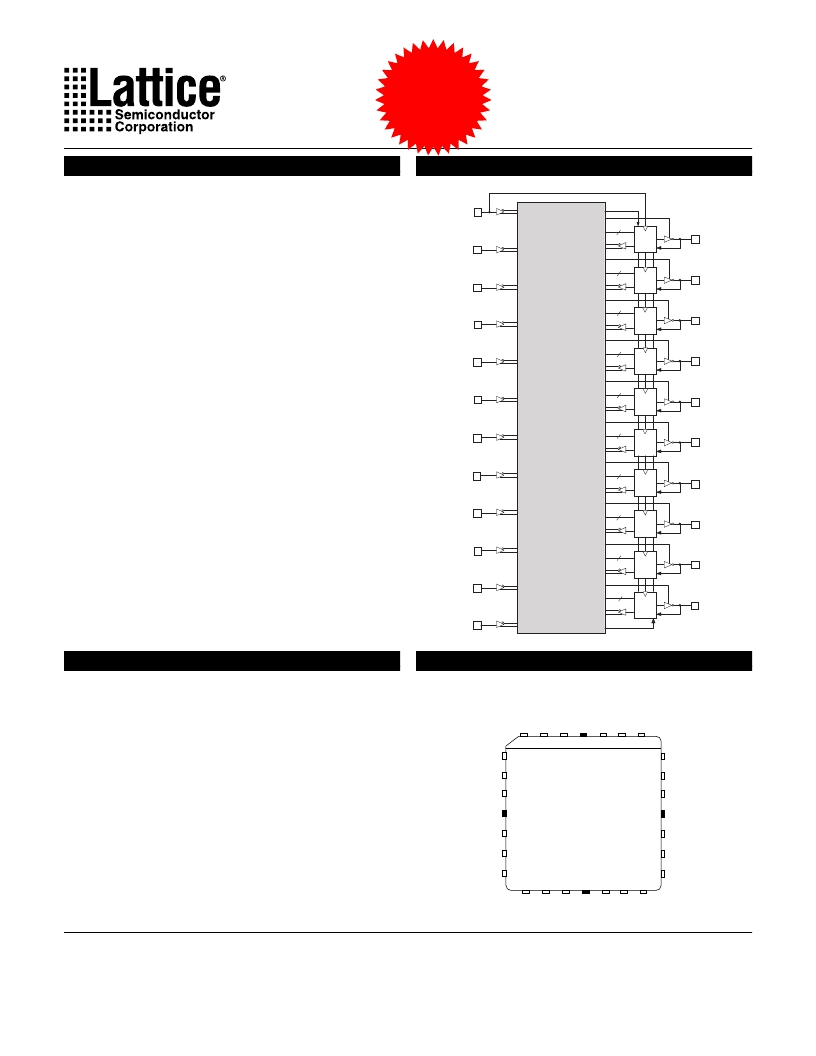

GAL22LV10

Low Voltage E

2

CMOS PLD

Generic Array Logic

2

28

N

I

I

I

I

I

I

I

I

I

NC

NC

N

G

I

I

I

I

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

V

I

I

I

4

26

25

19

18

21

23

16

14

12

11

9

7

5

Features

HIGH PERFORMANCE E

2

CMOS

TECHNOLOGY

— 4 ns Maximum Propagation Delay

— Fmax = 250 MHz

— 3 ns Maximum from Clock Input to Data Output

— UltraMOS

Advanced CMOS Technology

3.3V LOW VOLTAGE 22V10 ARCHITECTURE

— JEDEC-Compatible 3.3V Interface Standard

— 5V Compatible Inputs

— I/O Interfaces with Standard 5V TTL Devices

(GAL22LV10C)

ACTIVE PULL-UPS ON ALL PINS (GAL22LV10D)

E

2

CELL TECHNOLOGY

— Reconfigurable Logic

— Reprogrammable Cells

— 100% Tested/100% Yields

— High Speed Electrical Erasure (<100ms)

— 20 Year Data Retention

TEN OUTPUT LOGIC MACROCELLS

— Maximum Flexibility for Complex Logic Designs

— Programmable Output Polarity

PRELOAD AND POWER-ON RESET OF ALL REGISTERS

— 100% Functional Testability

APPLICATIONS INCLUDE:

— Glue Logic for 3.3V Systems

— DMA Control

— State Machine Control

— High Speed Graphics Processing

— Standard Logic Speed Upgrade

ELECTRONIC SIGNATURE FOR IDENTIFICATION

P

A

(

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I

I/CLK

I

I

I

I

I

I

I

I

I

I

RESET

PRESET

8

10

12

14

16

16

14

12

10

8

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

GAL22LV10

Top View

PLCC

Copyright 2002 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A.

Tel. (503) 268-8000; 1-800-LATTICE; FAX (503) 268-8556; http://www.latticesemi.com

June 2002

Description

The GAL22LV10D, at 4 ns maximum propagation delay time, pro-

vides the highest speed performance available in the PLD market.

The GAL22LV10C can interface with both 3.3V and 5V signal levels.

The GAL22LV10 is manufactured using Lattice Semiconductor's

advanced 3.3V E

2

CMOS process, which combines CMOS with

Electrically Erasable (E

2

) floating gate technology. High speed erase

times (

<

100ms) allow the devices to be reprogrammed quickly and

efficiently.

The generic architecture provides maximum design flexibility by

allowing the Output Logic Macrocell (OLMC) to be configured by

the user.

Unique test circuitry and reprogrammable cells allow complete AC,

DC, and functional testing during manufacture. As a result, Lattice

Semiconductor delivers 100% field programmability and function-

ality of all GAL products. In addition, 100 erase/write cycles and

data retention in excess of 20 years are specified.

22lv10_05

New 5V

Inputs on

Tolerant

22LV10D

Functional Block Diagram

Pin Configuration

相關PDF資料 |

PDF描述 |

|---|---|

| GAL22V10-25LVC | Electrically-Erasable PLD |

| GAL22V10-30LNI | Electrically-Erasable PLD |

| GAL22LV10C-15J | IC-SM-CMOS PLD |

| GAL22LV10C-15LJ | Electrically-Erasable PLD |

| GAL22LV10C-15LJI | Electrically-Erasable PLD |

相關代理商/技術參數 |

參數描述 |

|---|---|

| GAL22V10-25LR/883 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| GAL22V10-25LVC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| GAL22V10-25LVI | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:GENERIC ARRAY LOGIC |

| GAL22V10-25LVM | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:GENERIC ARRAY LOGIC |

| GAL22V10-25P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

發布緊急采購,3分鐘左右您將得到回復。