- 您現在的位置:買賣IC網 > PDF目錄385318 > GS8322V72GC-133I (GSI TECHNOLOGY) 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs PDF資料下載

參數資料

| 型號: | GS8322V72GC-133I |

| 廠商: | GSI TECHNOLOGY |

| 元件分類: | DRAM |

| 英文描述: | 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs |

| 中文描述: | 512K X 72 CACHE SRAM, 8.5 ns, PBGA209 |

| 封裝: | 14 X 22 MM, 1 MM PITCH, LEAD FREE, BGA-209 |

| 文件頁數: | 31/42頁 |

| 文件大小: | 1038K |

| 代理商: | GS8322V72GC-133I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Preliminary

GS8322V18(B/E)/GS8322V36(B/E)/GS8322V72(C)

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 1.04 4/2005

31/42

2003, GSI Technology

Typically, the Boundary Scan Register is loaded with the desired pattern of data with the SAMPLE/PRELOAD command.

Then the EXTEST command is used to output the Boundary Scan Register’s contents, in parallel, on the RAM’s data output

drivers on the falling edge of TCK when the controller is in the Update-IR state.

Alternately, the Boundary Scan Register may be loaded in parallel using the EXTEST command. When the EXTEST instruc-

tion is selected, the sate of all the RAM’s input and I/O pins, as well as the default values at Scan Register locations not asso-

ciated with a pin, are transferred in parallel into the Boundary Scan Register on the rising edge of TCK in the Capture-DR

state, the RAM’s output pins drive out the value of the Boundary Scan Register location with which each output pin is associ-

ated.

IDCODE

The IDCODE instruction causes the ID ROM to be loaded into the ID register when the controller is in Capture-DR mode and

places the ID register between the TDI and TDO pins in Shift-DR mode. The IDCODE instruction is the default instruction

loaded in at power up and any time the controller is placed in the Test-Logic-Reset state.

SAMPLE-Z

If the SAMPLE-Z instruction is loaded in the instruction register, all RAM outputs are forced to an inactive drive state (high-

Z) and the Boundary Scan Register is connected between TDI and TDO when the TAP controller is moved to the Shift-DR

state.

RFU

These instructions are Reserved for Future Use. In this device they replicate the BYPASS instruction.

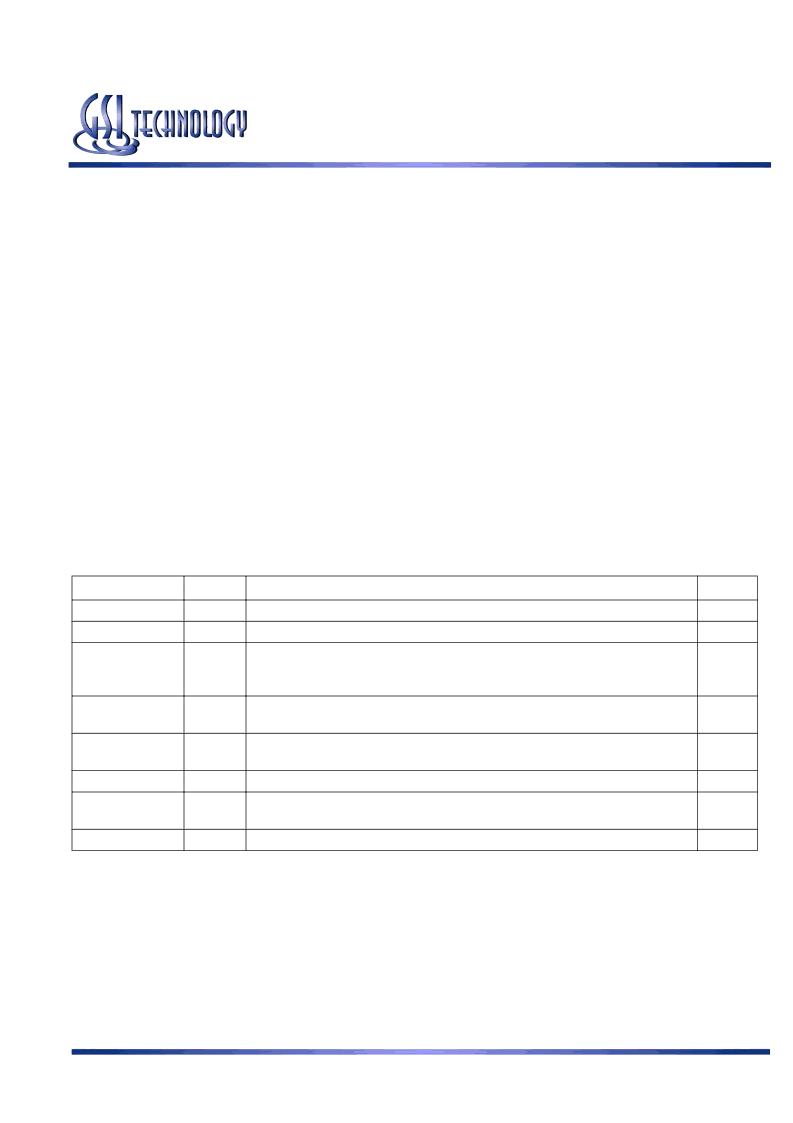

JTAG TAP Instruction Set Summary

Instruction

Code

Description

Notes

EXTEST

000

Places the Boundary Scan Register between TDI and TDO.

1

IDCODE

001

Preloads ID Register and places it between TDI and TDO.

1, 2

SAMPLE-Z

010

Captures I/O ring contents. Places the Boundary Scan Register between TDI and

TDO.

Forces all RAM output drivers to High-Z.

Do not use this instruction; Reserved for Future Use.

Replicates BYPASS instruction. Places Bypass Register between TDI and TDO.

Captures I/O ring contents. Places the Boundary Scan Register between TDI and

TDO.

1

RFU

011

1

SAMPLE/

PRELOAD

100

1

GSI

101

GSI private instruction.

1

RFU

110

Do not use this instruction; Reserved for Future Use.

Replicates BYPASS instruction. Places Bypass Register between TDI and TDO.

Places Bypass Register between TDI and TDO.

1

BYPASS

111

1

Notes:

1.

2.

Instruction codes expressed in binary, MSB on left, LSB on right.

Default instruction automatically loaded at power-up and in test-logic-reset state.

相關PDF資料 |

PDF描述 |

|---|---|

| GS8322V72GC-150 | 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs |

| GS8322V72GC-150I | 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs |

| GS8322V72GC-166 | 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs |

| GS8322V72GC-166I | 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs |

| GS8322V72GC-200 | 2M x 18, 1M x 36, 512K x 72 36Mb S/DCD Sync Burst SRAMs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| GS8322V72GC-200 | 制造商:GSI Technology 功能描述:SRAM SYNC OCTAL 1.8V 36MBIT 512KX72 7.5NS/3NS 209FBGA - Trays |

| GS8322V72GC-250 | 制造商:GSI Technology 功能描述:SRAM SYNC OCTAL 1.8V 36MBIT 512KX72 6.5NS/3NS 209FBGA - Trays |

| GS8322Z18AB-200I | 制造商:GSI Technology 功能描述:119 BGA - Bulk |

| GS8322Z18AB-200IV | 制造商:GSI Technology 功能描述:165 BGA - Bulk |

| GS8322Z18AB-200V | 制造商:GSI Technology 功能描述:165 BGA - Bulk |

發布緊急采購,3分鐘左右您將得到回復。