- 您現在的位置:買賣IC網 > PDF目錄385321 > GS8322ZV36B-250 (GSI TECHNOLOGY) 36Mb Pipelined and Flow Through Synchronous NBT SRAM PDF資料下載

參數資料

| 型號: | GS8322ZV36B-250 |

| 廠商: | GSI TECHNOLOGY |

| 元件分類: | DRAM |

| 英文描述: | 36Mb Pipelined and Flow Through Synchronous NBT SRAM |

| 中文描述: | 1M X 36 ZBT SRAM, 6.5 ns, PBGA119 |

| 封裝: | 14 X 22 MM, 1.27 PITCH, FPBGA-119 |

| 文件頁數: | 12/39頁 |

| 文件大小: | 975K |

| 代理商: | GS8322ZV36B-250 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

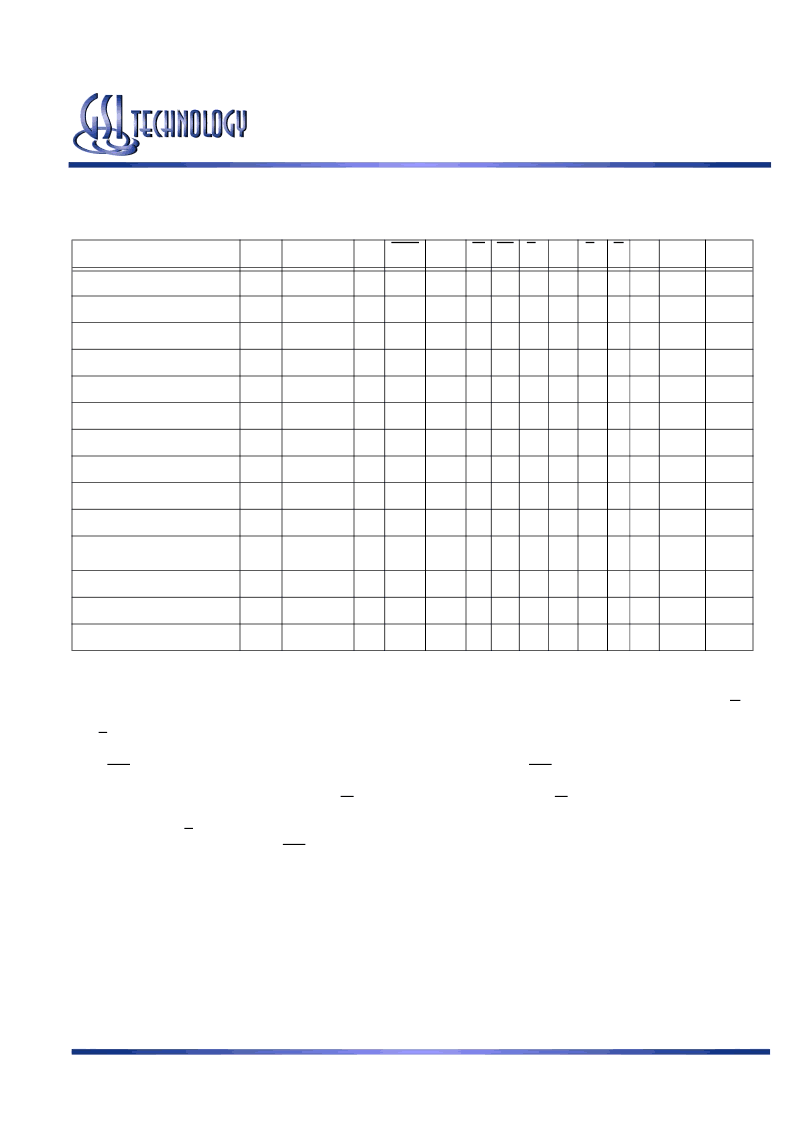

Synchronous Truth Table

Operation

Type

Address

CK CKE ADV W Bx E

1

E

2

E

3

G ZZ

DQ

Notes

Read Cycle, Begin Burst

R

External

L-H

L

L

H

X

L

H

L

L

L

Q

Read Cycle, Continue Burst

B

Next

L-H

L

H

X

X

X

X

X

L

L

Q

1,10

NOP/Read, Begin Burst

R

External

L-H

L

L

H

X

L

H

L

H

L

High-Z

2

Dummy Read, Continue Burst

B

Next

L-H

L

H

X

X

X

X

X

H

L

High-Z

1,2,10

Write Cycle, Begin Burst

W

External

L-H

L

L

L

L

L

H

L

X

L

D

3

Write Cycle, Continue Burst

B

Next

L-H

L

H

X

L

X

X

X

X

L

D

1,3,10

Write Abort, Continue Burst

B

Next

L-H

L

H

X

H

X

X

X

X

L

High-Z 1,2,3,10

Deselect Cycle, Power Down

D

None

L-H

L

L

X

X

H

X

X

X

L

High-Z

Deselect Cycle, Power Down

D

None

L-H

L

L

X

X

X

X

H

X

L

High-Z

Deselect Cycle, Power Down

D

None

L-H

L

L

X

X

X

L

X

X

L

High-Z

Deselect Cycle

D

None

L-H

L

L

L

H

L

H

L

X

L

High-Z

1

Deselect Cycle, Continue

D

None

L-H

L

H

X

X

X

X

X

X

L

High-Z

1

Sleep Mode

None

X

X

X

X

X

X

X

X

X

H

High-Z

Clock Edge Ignore, Stall

Current

L-H

H

X

X

X

X

X

X

X

L

-

4

Notes:

1.

Continue Burst cycles, whether read or write, use the same control inputs. A Deselect continue cycle can only be entered into if a Dese-

lect cycle is executed first.

Dummy Read and Write abort can be considered NOPs because the SRAM performs no operation. A Write abort occurs when the W

pin is sampled low but no Byte Write pins are active so no write operation is performed.

G can be wired low to minimize the number of control signals provided to the SRAM. Output drivers will automatically turn off during

write cycles.

If CKE High occurs during a pipelined read cycle, the DQ bus will remain active (Low Z). If CKE High occurs during a write cycle, the bus

will remain in High Z.

X = Don’t Care; H = Logic High; L = Logic Low; Bx = High = All Byte Write signals are high; Bx = Low = One or more Byte/Write

signals are Low

All inputs, except G and ZZ must meet setup and hold times of rising clock edge.

Wait states can be inserted by setting CKE high.

This device contains circuitry that ensures all outputs are in High Z during power-up.

A 2-bit burst counter is incorporated.

10. The address counter is incriminated for all Burst continue cycles.

2.

3.

4.

5.

6.

7.

8.

9.

GS8322ZV18(B/E)/GS8322ZV36(B/E)/GS8322ZV72(C)

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 1.03a 2/2006

12/39

2002, GSI Technology

相關PDF資料 |

PDF描述 |

|---|---|

| GS8322ZV36B-250I | 36Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8322ZV36E-133 | 36Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8322ZV36E-133I | 36Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8322ZV36E-150 | 36Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8322ZV36E-150I | 36Mb Pipelined and Flow Through Synchronous NBT SRAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| GS8322ZV72C-133 | 制造商:GSI Technology 功能描述:SRAM SYNC OCTAL 1.8V 36MBIT 512KX72 8.5NS/4NS 209FBGA - Trays |

| GS8322ZV72C-150 | 制造商:GSI Technology 功能描述:SRAM SYNC OCTAL 1.8V 36MBIT 512KX72 8.5NS/3.8NS 209FBGA - Trays |

| GS8322ZV72C-166 | 制造商:GSI Technology 功能描述:SRAM SYNC OCTAL 1.8V 36MBIT 512KX72 8NS/3.5NS 209FBGA - Trays |

| GS8324Z36B-133 | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 2.5V/3.3V 36MBIT 1MX36 10NS/4NS 119FBGA - Trays |

| GS8324Z36B-200I | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 2.5V/3.3V 36MBIT 1MX36 7.5NS/3NS 119FBGA - Trays |

發布緊急采購,3分鐘左右您將得到回復。