- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385328 > GS8640ZV18T-200I (GSI TECHNOLOGY) 72Mb Pipelined and Flow Through Synchronous NBT SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | GS8640ZV18T-200I |

| 廠商: | GSI TECHNOLOGY |

| 元件分類: | DRAM |

| 英文描述: | 72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| 中文描述: | 4M X 18 ZBT SRAM, 7.5 ns, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁(yè)數(shù): | 11/23頁(yè) |

| 文件大?。?/td> | 450K |

| 代理商: | GS8640ZV18T-200I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)

GS8640ZV18/36T-300/250/200/167

Product Preview

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 1.00 9/2004

11/23

2004, GSI Technology

Burst Cycles

Although NBT RAMs are designed to sustain 100% bus bandwidth by eliminating turnaround cycle when there is transition from

read to write, multiple back-to-back reads or writes may also be performed. NBT SRAMs provide an on-chip burst address

generator that can be utilized, if desired, to further simplify burst read or write implementations. The ADV control pin, when

driven high, commands the SRAM to advance the internal address counter and use the counter generated address to read or write

the SRAM. The starting address for the first cycle in a burst cycle series is loaded into the SRAM by driving the ADV pin low, into

Load mode.

Burst Order

The burst address counter wraps around to its initial state after four addresses (the loaded address and three more) have been

accessed. The burst sequence is determined by the state of the Linear Burst Order pin (LBO). When this pin is low, a linear burst

sequence is selected. When the RAM is installed with the LBO pin tied high, Interleaved burst sequence is selected. See the tables

below for details.

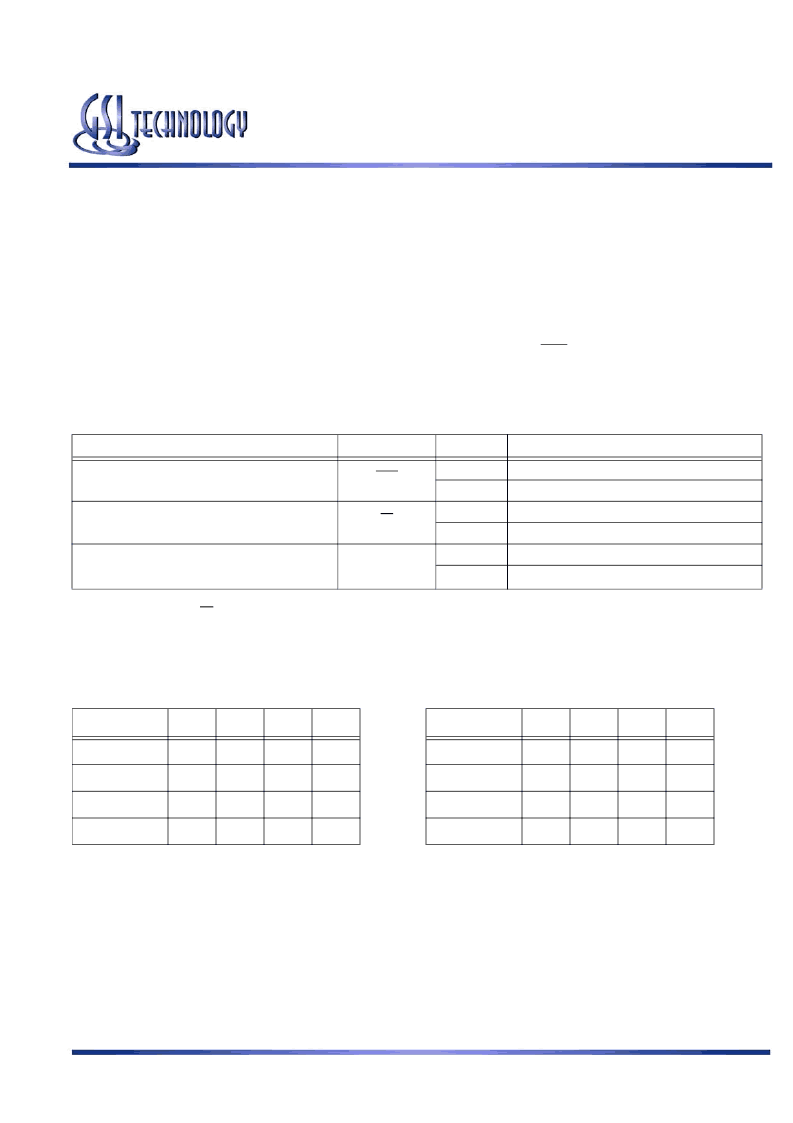

Mode Pin Functions

Note:

There is a pull-up device FT pin and a pull-down device on the ZZ pin, so those input pins can be unconnected and the chip will operate in the

default states as specified in the above tables.

Burst Counter Sequences

BPR 1999.05.18

Mode Name

Pin Name

State

L

H

L

H or NC

L or NC

Function

Linear Burst

Interleaved Burst

Flow Through

Pipeline

Active

Standby, I

DD

= I

SB

Burst Order Control

LBO

Output Register Control

FT

Power Down Control

ZZ

H

Note:

The burst counter wraps to initial state on the 5th clock.

Note:

The burst counter wraps to initial state on the 5th clock.

Linear Burst Sequence

A[1:0] A[1:0] A[1:0] A[1:0]

1st address

00

01

10

11

2nd address

01

10

11

00

3rd address

10

11

00

01

4th address

11

00

01

10

Interleaved Burst Sequence

A[1:0] A[1:0] A[1:0] A[1:0]

1st address

00

01

10

11

2nd address

01

00

11

10

3rd address

10

11

00

01

4th address

11

10

01

00

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS8640ZV18T-250 | 72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8640ZV18T-250I | 72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8640ZV18T-300 | 72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8640ZV18T-300I | 72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8640ZV36GT-167 | 72Mb Pipelined and Flow Through Synchronous NBT SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS8640ZV18T-250 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8640ZV18T-250I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8640ZV18T-300 | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 1.8V 72MBIT 4MX18 5.5NS/2.3NS 100TQFP - Trays |

| GS8640ZV18T-300I | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 1.8V 72MBIT 4MX18 5.5NS/2.3NS 100TQFP - Trays |

| GS8640ZV36GT-167 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Pipelined and Flow Through Synchronous NBT SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。