- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385332 > GS8644ZV18B-133I (GSI TECHNOLOGY) 72Mb Pipelined and Flow Through Synchronous NBT SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | GS8644ZV18B-133I |

| 廠商: | GSI TECHNOLOGY |

| 元件分類: | DRAM |

| 英文描述: | 72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| 中文描述: | 4M X 18 ZBT SRAM, 8.5 ns, PBGA119 |

| 封裝: | 14 X 22 MM, 1.27 MM PITCH, FBGA-119 |

| 文件頁(yè)數(shù): | 26/37頁(yè) |

| 文件大小: | 776K |

| 代理商: | GS8644ZV18B-133I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)當(dāng)前第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)

Product Preview

GS8644ZV18(B/E)/GS8644ZV36(B/E)/GS8644ZV72(C)

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 1.03 11/2004

26/37

2003, GSI Technology

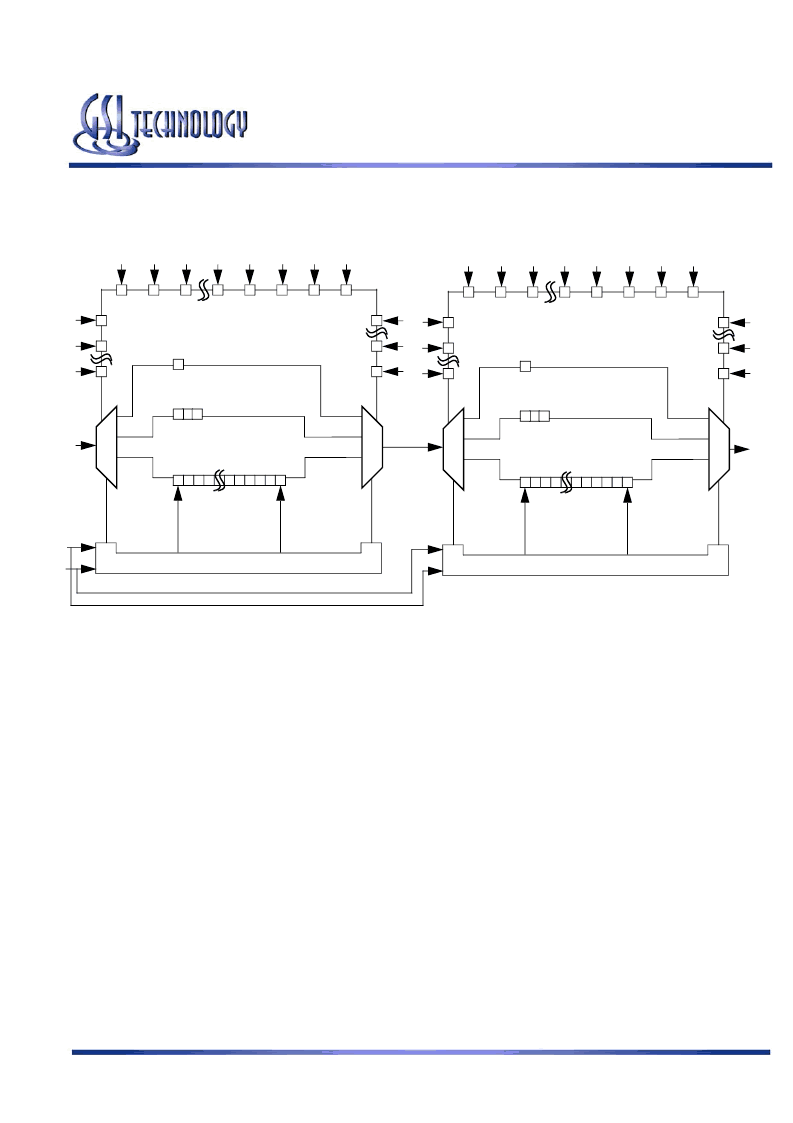

JTAG TAP Block Diagram (2-die module)

Identification (ID) Register

The ID Register is a 32-bit register that is loaded with a device and vendor specific 32-bit code when the controller is put in

Capture-DR state with the IDCODE command loaded in the Instruction Register. The code is loaded from a 32-bit on-chip ROM.

It describes various attributes of the RAM as indicated below. The register is then placed between the TDI and TDO pins when the

controller is moved into Shift-DR state. Bit 0 in the register is the LSB and the first to reach TDO when shifting begins.

Tap Controller Instruction Set

Overview

There are two classes of instructions defined in the Standard 1149.1-1990; the standard (Public) instructions, and device specific

(Private) instructions. Some Public instructions are mandatory for 1149.1 compliance. Optional Public instructions must be

implemented in prescribed ways. The TAP on this device may be used to monitor all input and I/O pads, and can be used to load

address, data or control signals into the RAM or to preload the I/O buffers.

When the TAP controller is placed in Capture-IR state the two least significant bits of the instruction register are loaded with 01.

When the controller is moved to the Shift-IR state the Instruction Register is placed between TDI and TDO. In this state the desired

instruction is serially loaded through the TDI input (while the previous contents are shifted out at TDO). For all instructions, the

TAP executes newly loaded instructions only when the controller is moved to Update-IR state. The TAP instruction set for this

device is listed in the following table.

Instruction Register

ID Code Register

·

31 30 29

Boundary Scan Register

0

1

2

0

· · ·

1

2

0

Bypass Register

TDI

TDO

TMS

TCK

Test Access Port (TAP) Controller

1

·

1

0

·

·

·

·

·

·

·

·

·

Control Signals

·

Instruction Register

ID Code Register

·

31 30 29

Boundary Scan Register

0

1

2

0

· · ·

1

2

0

Bypass Register

TDI

TDO

Test Access Port (TAP) Controller

1

·

1

0

·

·

·

·

·

·

·

·

·

Control Signals

·

··

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS8644ZV18B-150 | 72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8644ZV18B-150I | 72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8644ZV18B-166 | 72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8644ZV18B-166I | 72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8644ZV18B-200 | 72Mb Pipelined and Flow Through Synchronous NBT SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS8644ZV18B-150 | 制造商:GSI Technology 功能描述:SRAM SYNC QUAD 1.8V 72MBIT 4MX18 7.5NS/3.3NS 119FBGA - Trays |

| GS8644ZV18B-150I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8644ZV18B-166 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8644ZV18B-166I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Pipelined and Flow Through Synchronous NBT SRAM |

| GS8644ZV18B-200 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Pipelined and Flow Through Synchronous NBT SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。