- 您現在的位置:買賣IC網 > PDF目錄385337 > GS8662R36GE-333 (GSI TECHNOLOGY) 72Mb SigmaCIO DDR-II Burst of 4 SRAM PDF資料下載

參數資料

| 型號: | GS8662R36GE-333 |

| 廠商: | GSI TECHNOLOGY |

| 元件分類: | DRAM |

| 英文描述: | 72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| 中文描述: | 2M X 36 DDR SRAM, 0.45 ns, PBGA165 |

| 封裝: | 15 MM X 17 MM, 1 MM PITCH, ROHS COMPLIANT, FPBGA-165 |

| 文件頁數: | 8/37頁 |

| 文件大小: | 942K |

| 代理商: | GS8662R36GE-333 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

Preliminary

GS8662R08/09/18/36E-333/300/250/200/167

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 1.01 9/2005

8/37

2005, GSI Technology

Power-Up Sequence for SigmaQuad-II SRAMs

SigmaQuad-II SRAMs must be powered-up in a specific sequence in order to avoid undefined operations.

Power-Up Sequence

1. Power-up and maintain Doff at low state.

1a.

Apply V

DD

.

1b. Apply V

DDQ

.

1c. Apply V

REF

(may also be applied at the same time as V

DDQ

).

2. After power is achieved and clocks (K, K, C, C) are stablized, change Doff to high.

3. An additional 1024 clock cycles are required to lock the DLL after it has been enabled.

Note:

If you want to tie Doff high with an unstable clock, you must stop the clock for a minimum of 30 seconds to reset the DLL after the clocks become

stablized.

DLL Constraints

The DLL synchronizes to either K or C clock. These clocks should have low phase jitter (t

KCVar

on page 20).

The DLL cannot operate at a frequency lower than 119 MHz.

If the incoming clock is not stablized when DLL is enabled, the DLL may lock on the wrong frequency and cause undefined errors or failures during

the initial stage.

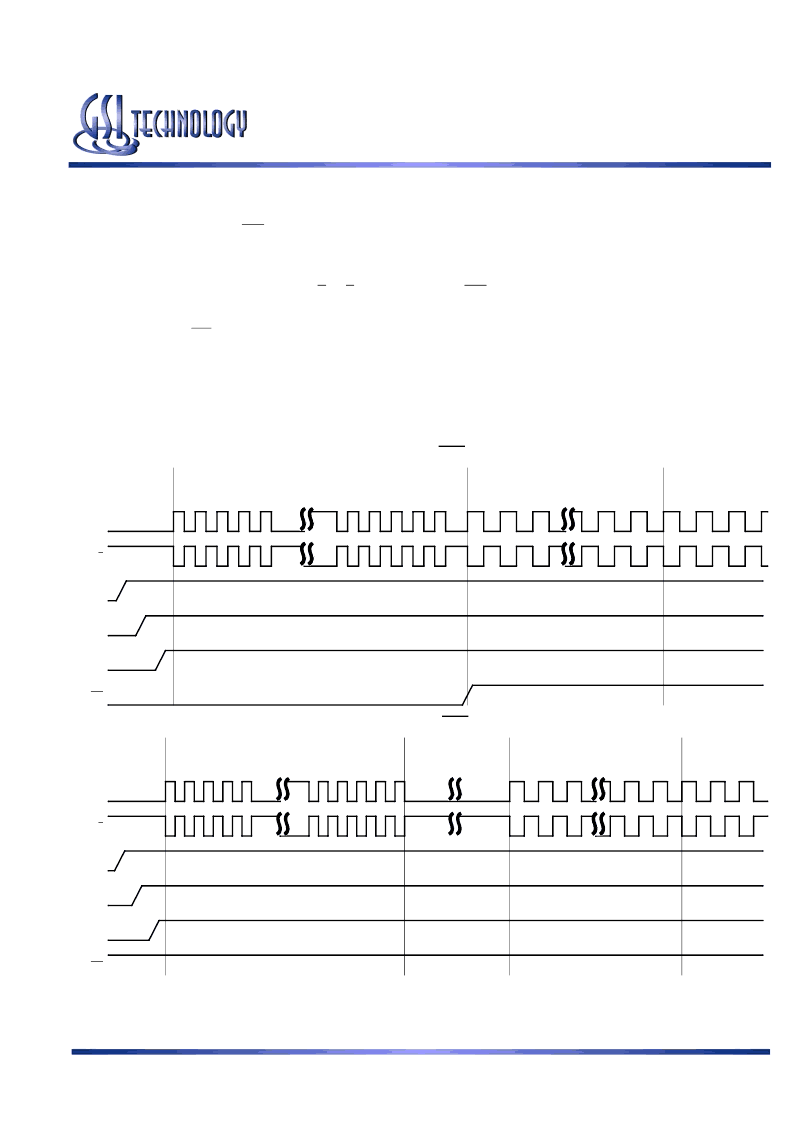

Power-Up Sequence (Doff controlled)

Power UP Interval

Unstable Clocking Interval

DLL Locking Interval (1024 Cycles)

Normal Operation

K

K

V

DD

V

DDQ

V

REF

Doff

Power-Up Sequence (Doff tied High)

Power UP Interval

Unstable Clocking Interval

Stop Clock Interval

30ns Min

DLL Locking Interval (1024 Cycles)

Normal Operation

K

K

V

DD

V

DDQ

V

REF

Doff

Note:

If the frequency is changed, DLL reset is required. After reset, a minimum of 1024 cycles is required for DLL lock.

相關PDF資料 |

PDF描述 |

|---|---|

| GS8662R36GE-333I | 72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| GS8662R08E | 72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| GS8662R08E-167 | 72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| GS8662R08E-167I | 72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| GS8662R08E-200 | 72Mb SigmaCIO DDR-II Burst of 4 SRAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| GS8662R36GE-333I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| GS8662S08BD-400 | 制造商:GSI Technology 功能描述:165 FBGA - Bulk |

| GS8662S08E | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Burst of 2 DDR SigmaSIO-II SRAM |

| GS8662S08E-167 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Burst of 2 DDR SigmaSIO-II SRAM |

| GS8662S08E-167I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb Burst of 2 DDR SigmaSIO-II SRAM |

發布緊急采購,3分鐘左右您將得到回復。