- 您現(xiàn)在的位置:買賣IC網 > PDF目錄369678 > GVT71128DA36T-4.4 x36 Fast Synchronous SRAM PDF資料下載

參數(shù)資料

| 型號: | GVT71128DA36T-4.4 |

| 英文描述: | x36 Fast Synchronous SRAM |

| 中文描述: | x36快速同步SRAM |

| 文件頁數(shù): | 1/24頁 |

| 文件大小: | 293K |

| 代理商: | GVT71128DA36T-4.4 |

256K x 18/128K x 36 Synchronous-Pipelined

Cache RAM

CY7C1347C/GVT71128DA36

CY7C1327C/GVT71256DA18

Cypress Semiconductor Corporation

3901 North First Street

San Jose

CA 95134

408-943-2600

July 21, 2000

Features

Fast access times: 2.5 and 3.5 ns

Fast clock speed: 250, 225, 200, and 166 MHz

1-ns set-up time and hold time

Fast OE access times: 2.5 ns and 3.5 ns

Optimal for depth expansion (one cycle chip deselect

to eliminate bus contention)

3.3V –5% and +10% power supply

3.3V or 2.5V I/O supply

5V tolerant inputs except I/Os

Clamp diodes to V

SS

at all inputs and outputs

Common data inputs and data outputs

Byte Write Enable and Global Write control

Three chip enables for depth expansion and address

pipeline

Address, data, and control registers

Internally self-timed Write Cycle

Burst control pins (interleaved or linear burst se-

quence)

Automatic power-down for portable applications

JTAG boundary scan

JEDEC standard pinout

Low profile 119-lead, 14-mm x 22-mm BGA (Ball Grid

Array) and 100-pin TQFP packages

Functional Description

The Cypress Synchronous Burst SRAM family employs

high-speed, low-power CMOS designs using advanced tri-

ple-layer polysilicon, double-layer metal technology. Each

memory cell consists of four transistors and two high-valued

resistors.

The

GVT71256DA18

262,144x18 SRAM cells with advanced synchronous periph-

eral circuitry and a 2-bit counter for internal burst operation. All

synchronous inputs are gated by registers controlled by a pos-

itive-edge-triggered clock input (CLK). The synchronous in-

puts include all addresses, all data inputs, address-pipelining

Chip Enable (CE), depth-expansion Chip Enables (CE2 and

CE2), Burst Control Inputs (ADSC, ADSP and ADV), Write

Enables (BWa, BWb, BWc, BWd, and BWE), and Global Write

(GW).

Asynchronous inputs include the Output Enable (OE) and

Burst Mode Control (MODE). The data outputs (Q), enabled

by OE, are also asynchronous.

Addresses and chip enables are registered with either Ad-

dress Status Processor (ADSP) or Address Status Controller

(ADSC) input pins. Subsequent burst addresses can be inter-

nally generated as controlled by the Burst Advance pin (ADV).

Address, data inputs, and write controls are registered on-chip

to initiate self-timed Write cycle. Write cycles can be one to

four bytes wide as controlled by the write control inputs. Indi-

vidual byte write allows individual byte to be written. BWa con-

trols DQa. BWb controls DQb. BWc controls DQc. BWd con-

trols DQd. BWa, BWb, BWc, and BWd can be active only with

BWE being LOW. GW being LOW causes all bytes to be writ-

ten. The x18 version only has 18 data inputs/outputs (DQa and

DQb) along with BWa and BWb (no BWc, BWd, DQc, and

DQd).

Four pins are used to implement JTAG test capabilities: Test

Mode Select (TMS), Test Data-in (TDI), Test Clock (TCK), and

Test Data-out (TDO). The JTAG circuitry is used to serially shift

data to and from the device. JTAG inputs use LVTTL/LVCMOS

levels to shift data during this testing mode of operation.

The

CY7C1347C/GVT71128DA36

GVT71256DA18 operate from a +3.3V power supply. All inputs

and outputs are LVTTL compatible

CY7C1347C/GVT71128DA36

SRAMs

and

CYC7C1327C/

131,072x36

integrate

and

and

CY7C1327C/

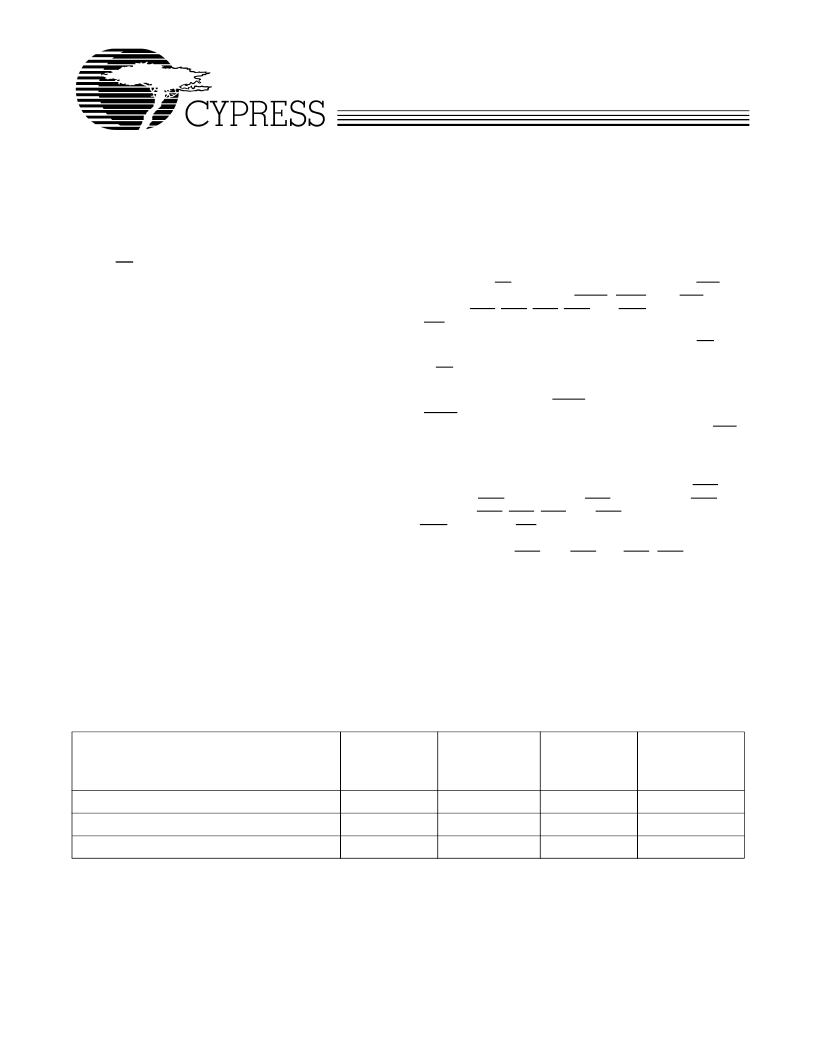

Selection Guide

7C1347C-250

71128DA36-4

7C1327C-250

71256DA18-4

7C1347C-225

71128DA36-4.4

7C1327C-225

71256DA18-4.4

7C1347C-200

71128DA36-5

7C1327C-200

71256DA18-5

7C1347C-166

71128DA36-6

7C1327C-166

71256DA18-6

Maximum Access Time (ns)

2.5

2.5

2.5

3.5

Maximum Operating Current (mA)

450

400

360

300

Maximum CMOS Standby Current (mA)

10

10

10

10

相關PDF資料 |

PDF描述 |

|---|---|

| GVT71128DA36T-5 | x36 Fast Synchronous SRAM |

| GVT71128DA36T-6 | x36 Fast Synchronous SRAM |

| GVT71128E36B-10 | x36 Fast Synchronous SRAM |

| GVT71128E36B-7 | x36 Fast Synchronous SRAM |

| GVT71128E36B-8 | x36 Fast Synchronous SRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| GVT71128DA36T-5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Fast Synchronous SRAM |

| GVT71128DA36T-6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Fast Synchronous SRAM |

| GVT71128E36B-10 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Fast Synchronous SRAM |

| GVT71128E36B-7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Fast Synchronous SRAM |

| GVT71128E36B-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Fast Synchronous SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。