- 您現在的位置:買賣IC網 > PDF目錄385354 > HC4053 (System Logic Semiconductor Co., Ltd.) IC-VLTG REG 125V-1A PDF資料下載

參數資料

| 型號: | HC4053 |

| 廠商: | System Logic Semiconductor Co., Ltd. |

| 英文描述: | IC-VLTG REG 125V-1A |

| 中文描述: | 模擬多路復用器/解復用器 |

| 文件頁數: | 5/8頁 |

| 文件大小: | 87K |

| 代理商: | HC4053 |

SL74HC4053

S ystem Logic

Semiconductor

SLS

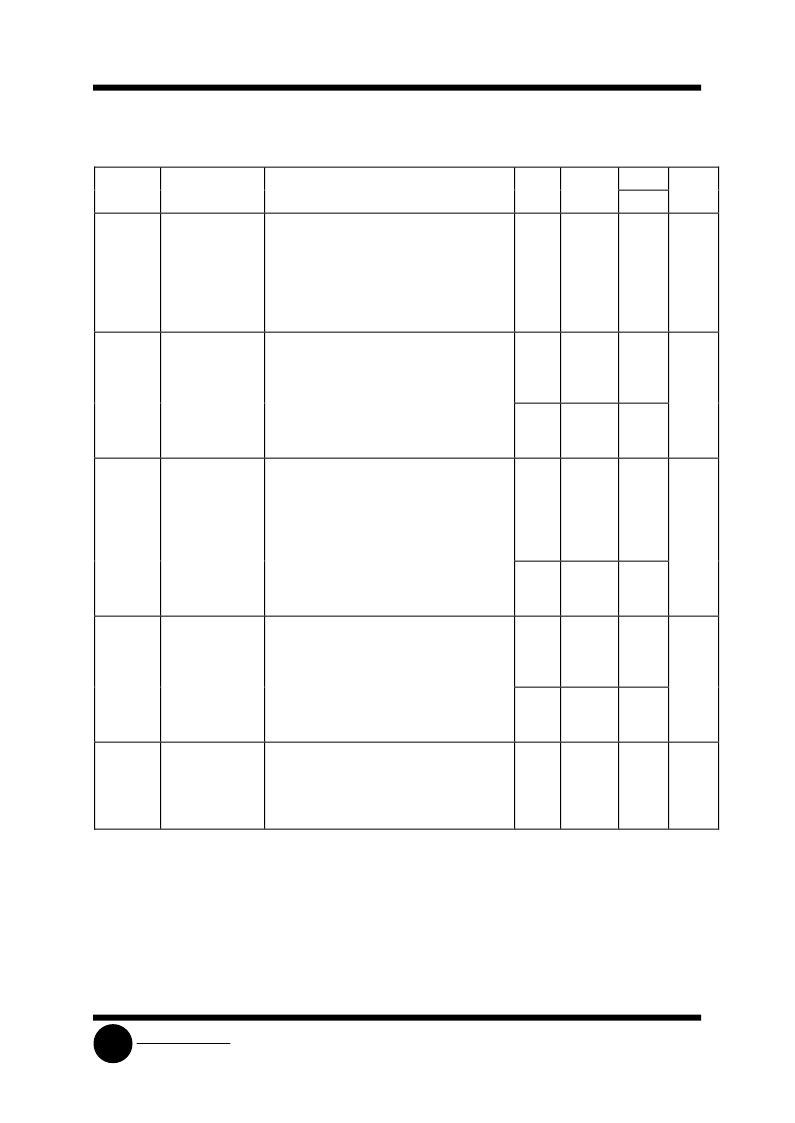

ADDITIONAL APPLICATION CHARACTERISTICS

(GND = 0.0 V)

V

CC

V

EE

Limit

*

Symbol

Parameter

Test Conditions

V

V

25

°

C

Unit

BW

Maximum On-

Channel

Bandwidth or

Minimum

Frequency

Response

(Figure 5)

f

in

=1 MHz Sine Wave

Adjust f

in

Voltage to Obtain 0 dBm at V

OS

Increase f

in

Frequence Until dB Meter

Reads -3 dB

R

L

=50

, C

L

=10 pF

2.25

4.50

6.00

-2.25

-4.50

-6.00

120

120

120

MHz

-

Off-Channel

Feedthrough

Isolation

(Figure 6)

f

in

= Sine Wave

Adjust f

in

Voltage to Obtain 0 dBm at V

IS

f

in

= 10 kHz, R

L

=600

, C

L

=50 pF

2.25

4.50

6.00

-2.25

-4.50

-6.00

-50

-50

-50

dB

f

in

= 1.0 MHz, R

L

=50

, C

L

=10 pF

2.25

4.50

6.00

-2.25

-4.50

-6.00

-40

-40

-40

-

Feedthrough

Noise, Channel

Select Input to

Common O/I

(Figure 7)

V

IN

≤

1 MHz Square Wave (t

r

= t

f

= 6 ns)

Adjust R

L

at Setup so that I

S

= 0 A Enable =

GND

R

L

=600

, C

L

=50 pF

2.25

4.50

6.00

-2.25

-4.50

-6.00

25

105

135

mVpp

R

L

=10

, C

L

=10 pF

2.25

4.50

6.00

-2.25

-4.50

-6.00

35

145

190

-

Crosstalk

Between Any

Two Switches

(Figure 14)

f

in

= Sine Wave

Adjust f

in

Voltage to Obtain 0 dBm at V

IS

f

in

= 10 kHz, R

L

=600

, C

L

=50 pF

2.25

4.50

6.00

-2.25

-4.50

-6.00

-50

-50

-50

dB

f

in

= 1 MHz, R

L

=50

, C

L

=10 pF

2.25

4.50

6.00

-2.25

-4.50

-6.00

-60

-60

-60

THD

Total Harmonic

Distortion

(Figure 16)

f

in

= 1 kHz, R

L

=10 k

, C

L

=50 pF

THD = THD

Measured

- THD

Source

V

IS

=4.0 V

PP

sine wave

V

IS

=8.0 V

PP

sine wave

V

IS

=11.0 V

PP

sine wave

2.25

4.50

6.00

-2.25

-4.50

-6.00

0.10

0.08

0.05

%

* Limits not tested. Determined by design and verified by qualification.

相關PDF資料 |

PDF描述 |

|---|---|

| HC4094 | T-NPN-SI HIGH VLTG AMP |

| HC49J | SM Crystal Formed Leads |

| HC534 | Voltage Regulator IC; Package/Case:3-TO-3; Current Rating:1.5A; Output Voltage Max:-12V; Voltage Regulator Type:Fixed Voltage; Mounting Type:Through Hole |

| HC5503CBZ | Low Cost 24V SLIC For PABX / Key Systems |

| HC5503CBZ96 | Low Cost 24V SLIC For PABX / Key Systems |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HC4054 | 制造商:HUASHAN 制造商全稱:HUASHAN 功能描述:NPN SILICON TRANSISTOR |

| HC4056B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| HC-406 | 制造商:Thomas & Betts 功能描述: |

| HC4060 | 制造商:n/a 功能描述:CGE125X030 |

| HC4060 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。