- 您現在的位置:買賣IC網 > PDF目錄385382 > HIP6020EVAL1 (Intersil Corporation) Advanced Dual PWM and Dual Linear Power Controller PDF資料下載

參數資料

| 型號: | HIP6020EVAL1 |

| 廠商: | Intersil Corporation |

| 元件分類: | 基準電壓源/電流源 |

| 英文描述: | Advanced Dual PWM and Dual Linear Power Controller |

| 中文描述: | 先進的雙PWM和線性雙電源控制器 |

| 文件頁數: | 9/15頁 |

| 文件大小: | 139K |

| 代理商: | HIP6020EVAL1 |

2-289

MOSFET switching. The over-current function will trip at a peak

inductor current (I

PEAK)

determined by:

The OC trip point varies with MOSFET’s rDS(ON)

temperature variations. To avoid over-current tripping in the

normal operating load range, determine the ROCSET

resistor value from the equation above with:

1. The maximum r

DS(ON)

at the highest junction temperature

2. The minimum I

OCSET

from the specification table

3. Determine I

PEAK

for I

PEAK

> I

OUT(MAX)

+ (

I)/2,

where

I is the output inductor ripple current.

For an equation for the ripple current see the section under

component guidelines titled ‘Output Inductor Selection’.

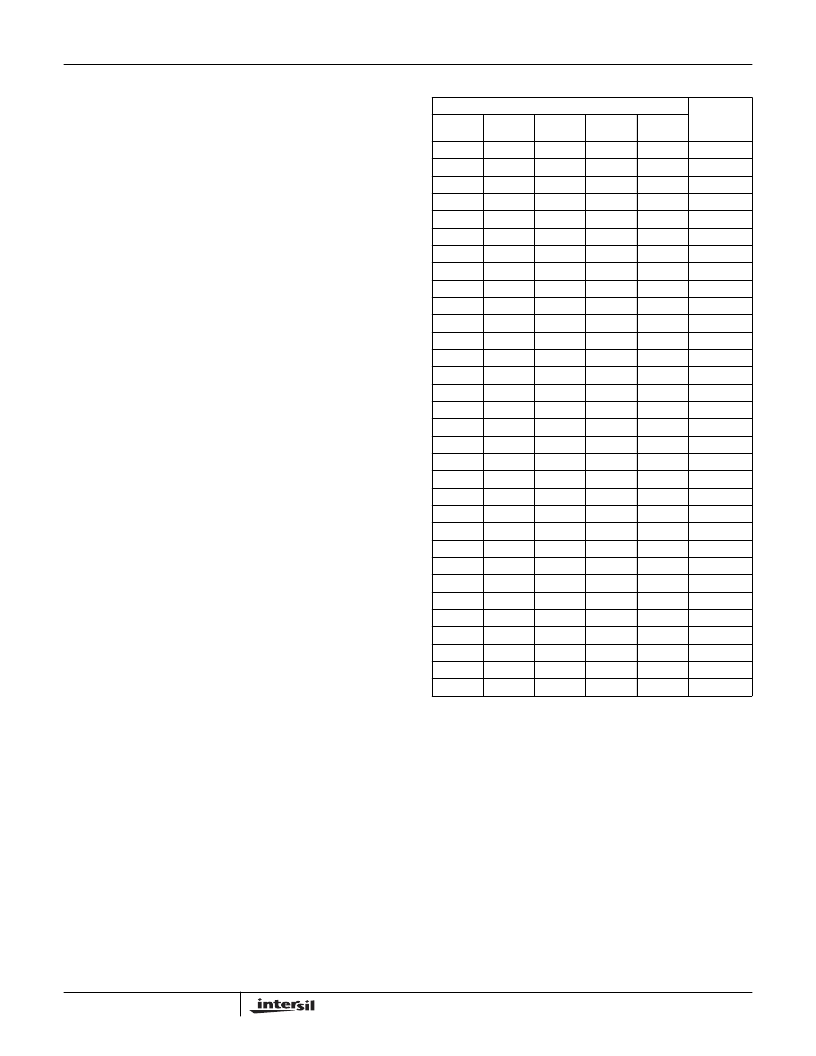

OUT1 Voltage Program

The output voltage of the PWM1 converter is programmed to

discrete levels between 1.3V

DC

and 3.5V

DC

. This output

(OUT1) is designed to supply the core voltage of Intel’s

advanced microprocessors. The voltage identification (VID)

pins program an internal voltage reference (DACOUT) with a

TTL-compatible 5-bit digital-to-analog converter (DAC). The

level of DACOUT also sets the PGOOD and OVP thresholds.

Table 1 specifies the DACOUT voltage for the different

combinations of connections on the VID pins. The VID pins

can be left open for a logic 1 input, because they are internally

pulled up to an internal voltage of about 5V by a 10

μ

A current

source. Changing the VID inputs during operation is not

recommended and could toggle the PGOOD signal and

exercise the over-voltage protection. ‘11111’ VID pin

combination disables the IC and opens the PGOOD pin.

OUT2 Voltage Selection

The AGP regulator output voltage is internally set to one of

two discrete levels, based on the status of the SELECT pin.

SELECT pin is internally pulled ‘high’, such that left open,

the AGP output voltage is by default set to 3.3V. The other

discrete setting available is 1.5V, which can be obtained by

grounding the SELECT pin using a jumper or another

suitable method capable of sinking a few tens of

microamperes. The status of the SELECT pin cannot be

changed during operation of the IC without immediately

causing a fault condition.

Application Guidelines

Soft-Start Interval

Initially,thesoft-startfunctionclampstheerroramplifier’soutput

of the PWM converters. This generates PHASE pulses of

increasing width that charge the output capacitor(s). After the

output voltage increases to approximately 70% of the set value,

the reference input of the error amplifier is clamped to a voltage

proportionaltotheSSpinvoltage.Theresultingoutputvoltages

start-up as shown in Figure 6.

The soft-start function controls the output voltage rate of rise

to limit the current surge at start-up. The soft-start interval

and the surge current are programmed by the soft-start

capacitor, C

SS

. Programming a faster soft-start interval

I

PEAK

=

I

---------------------------------------------------

R

×

DS ON

)

TABLE 1. OUT1 VOLTAGE PROGRAM

PIN NAME

NOMINAL

DACOUT

VOLTAGE

1.30

1.35

1.40

1.45

1.50

1.55

1.60

1.65

1.70

1.75

1.80

1.85

1.90

1.95

2.00

2.05

0

2.1

2.2

2.3

2.4

2.5

2.6

2.7

2.8

2.9

3.0

3.1

3.2

3.3

3.4

3.5

VID4

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

VID3

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

VID2

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

VID1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

VID0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

NOTE: 0 = connected to GND, 1 = open or connected to 5V through

pull-up resistors

HIP6020

相關PDF資料 |

PDF描述 |

|---|---|

| HIP6020 | FPGA - 100000 SYSTEM GATE 2.5 VOLT - NOT RECOMMENDED for NEW DESIGN |

| HIP6020CB | Advanced Dual PWM and Dual Linear Power Controller |

| HIP6301VCBZ-T | 100000 SYSTEM GATE 1.8 VOLT FPGA - NOT RECOMMENDED for NEW DESIGN |

| HIP6301VCBZA | Microprocessor CORE Voltage Regulator Multi-Phase Buck PWM Controller |

| HIP6301VCBZA-T | 150000 SYSTEM GATE 2.5 VOLT FPGA - NOT RECOMMENDED for NEW DESIGN |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HIP6021 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Advanced PWM and Triple Linear Power Controller |

| HIP6021_05 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Advanced PWM and Triple Linear Power Controller |

| HIP6021A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Advanced PWM and Triple Linear Power Controller |

| HIP6021A_01 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Advanced PWM and Triple Linear Power Controller |

| HIP6021ACB | 制造商:Rochester Electronics LLC 功能描述:4IN1 1PWM, 3 LINEARS, 28L SOIC, 5 BIT DAC - Bulk |

發布緊急采購,3分鐘左右您將得到回復。