- 您現在的位置:買賣IC網 > PDF目錄385382 > HIP6502 (Intersil Corporation) Multiple Linear Power Controller with ACPI Control Interface PDF資料下載

參數資料

| 型號: | HIP6502 |

| 廠商: | Intersil Corporation |

| 元件分類: | 基準電壓源/電流源 |

| 英文描述: | Multiple Linear Power Controller with ACPI Control Interface |

| 中文描述: | 多重線性電源控制器ACPI控制接口 |

| 文件頁數: | 7/14頁 |

| 文件大小: | 147K |

| 代理商: | HIP6502 |

7

5VDLSB (Pin 14)

Connect this pin to the gate of a suitable P-MOSFET or

bipolar PNP. In sleep state, this transistor is switched on,

connecting the ATX 5VSB output to the 5V

DUAL

regulator

output.

VSEN1 (Pin 3)

Connect this pin to the 3.3V memory output (V

OUT1

). In

sleep states, this pin is regulated to 3.3V through an internal

pass transistor capable of delivering 300mA (typically). The

active-state voltage at this pin is provided from the ATX 3.3V

through a fully on external N-MOS transistor. During all

operating states, the voltage at this pin is monitored for

under-voltage events.

VCLK (Pin 6)

This pin is the output of the internal 2.5V clock chip regulator

(V

OUT4

). This internal regulator operates only in active

states (S0, S1/S2) and is shut off during any sleep state,

regardless of the configuration of the chip. This pin is

monitored for under-voltage events.

Description

Operation

The HIP6502 controls 5 output voltages (Refer to Figures 1,

2, and 3). It is designed for microprocessor computer

applications with 3.3V, 5V, 5VSB, and 12V bias input from an

ATX power supply. The IC is composed of three linear

controllers/regulators supplying the computer system’s

3.3V

SB

and PCI slots’ 3.3V

AUX

power (V

OUT3

), the 2.5V

RDRAM and 3.3V SDRAM memory power (V

OUT2

, V

OUT1

),

an integrated regulator dedicated to 2.5V clock chip

(V

OUT4

), a dual switch controller supplying the 5V

DUAL

voltage (V

OUT5

), as well as all the control and monitoring

functions necessary for complete ACPI implementation.

Initialization

The HIP6502 automatically initializes upon receipt of input

power. The Power-On Reset (POR) function continually

monitors the 5VSB input supply voltage, initiating 3.3V

SB

soft-start operation after exceeding POR threshold. At 3ms

(typically) after 3.3V

SB

finishes its ramp-up, the EN5VDL

status is latched in and the chip proceeds to ramp up the

remainder of the voltages, as required.

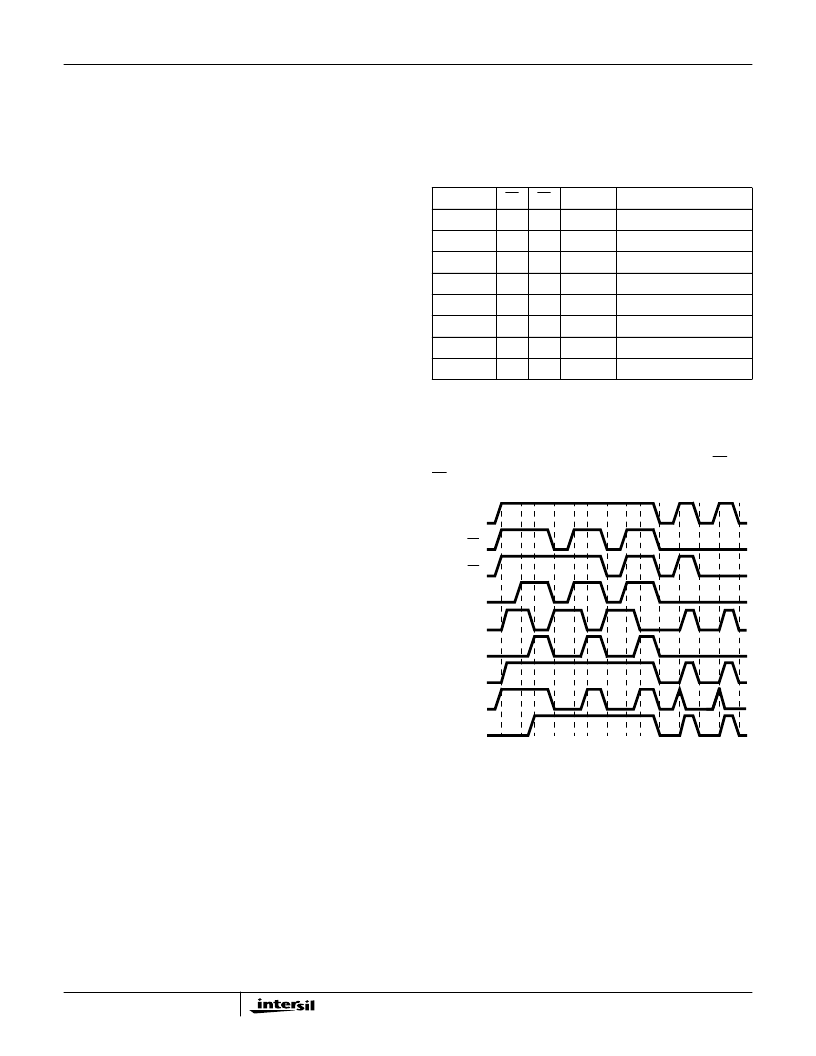

Operational Truth Table

The EN5VDL pin offers the choice of supporting or disabling

5VDUAL output in S3 and S4/S5 sleep states. Table 1

describes the truth combinations pertaining to this output.

Not shown in any of the tables are the 3.3V

DUAL

/3.3V

SB

and

the 2.5V

CLK

outputs. The 3.3V

DUAL

/3.3V

SB

output powers

up as soon as the 5VSB ATX output is available. The

2.5V

CLK

output operation is restricted by the chip’s POR and

is only available in active state (S0, S1). For additional

information, see the soft-start sequence diagrams.

Additionally, the internal circuitry does not allow the

transition from an S3 (suspend to RAM) state to an S4/S5

(suspend to disk/soft off) state or vice versa. The only ‘legal’

transitions are from an active state (S0, S1) to a sleep state

(S3, S5) and vice versa.

Functional Timing Diagrams

Figures 4 through 6 are timing diagrams, detailing the power

up/down sequences of all three outputs in response to the

status of the enable (EN5VDL) and sleep-state pins (S3,

S5), as well as the status of the ATX supply.

The status of the EN5VDL pin can only be changed while in

active (S0, S1) states, when the bias supply (5VSB pin) is

below POR level, or during chip shutdown (SS pin shorted to

GND or within 3ms of 5VSB POR); a status change of this

pin while in a sleep state is ignored.

TABLE 1. 5V

DUAL

OUTPUT (V

OUT5

) TRUTH TABLE

EN5VDL

S5

S3

5VDL

COMMENTS

0

1

1

5V

S0, S1 States (Active)

0

1

0

0V

S3

0

0

1

Note

Maintains Previous State

0

0

0

0V

S4/S5

1

1

1

5V

S0, S1 States (Active)

1

1

0

5V

S3

1

0

1

Note

Maintains Previous State

1

0

0

5V

S4/S5

NOTE: Combination Not Allowed.

FIGURE 4. 5V

DUAL

TIMING DIAGRAM FOR EN5VDL = 1;

3.3V

DUAL

/3.3V

SB

5VSB

3.3V,

S3

S5

5VDLSB

DLA

3V3DLSB

3V3DL

5VDL

5V, 12V

HIP6502

相關PDF資料 |

PDF描述 |

|---|---|

| HIP6502CB | Multiple Linear Power Controller with ACPI Control Interface |

| HIP6503EVAL1 | Multiple Linear Power Controller with ACPI Control Interface |

| HIP6503CB | Circular Connector; No. of Contacts:37; Series:MS27467; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:15; Circular Contact Gender:Socket; Circular Shell Style:Straight Plug; Insert Arrangement:15-35 |

| HIP6503 | Multiple Linear Power Controller with ACPI Control Interface(集成了多個線性電源控制器的芯片(ACPI控制接口)) |

| HIP6602ACB | FPGA 1600000 SYSTEM GATE 1.8 VOLT - NOT RECOMMENDED for NEW DESIGN |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HIP6502 WAF | 制造商:Intersil Corporation 功能描述: |

| HIP6502_00 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Multiple Linear Power Controller with ACPI Control Interface |

| HIP6502B | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Multiple Linear Power Controller with ACPI Control Interface |

| HIP6502BCB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP6502BEVAL1 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Multiple Linear Power Controller with ACPI Control Interface |

發布緊急采購,3分鐘左右您將得到回復。