- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385393 > HS1-80C85RH-8 (INTERSIL CORP) Radiation Hardened 8-Bit CMOS Microprocessor PDF資料下載

參數(shù)資料

| 型號: | HS1-80C85RH-8 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Radiation Hardened 8-Bit CMOS Microprocessor |

| 中文描述: | 8-BIT, 2 MHz, MICROPROCESSOR, CDIP40 |

| 封裝: | SIDE BRAZED, METAL SEALED, CERAMIC, DIP-40 |

| 文件頁數(shù): | 15/16頁 |

| 文件大小: | 758K |

| 代理商: | HS1-80C85RH-8 |

15

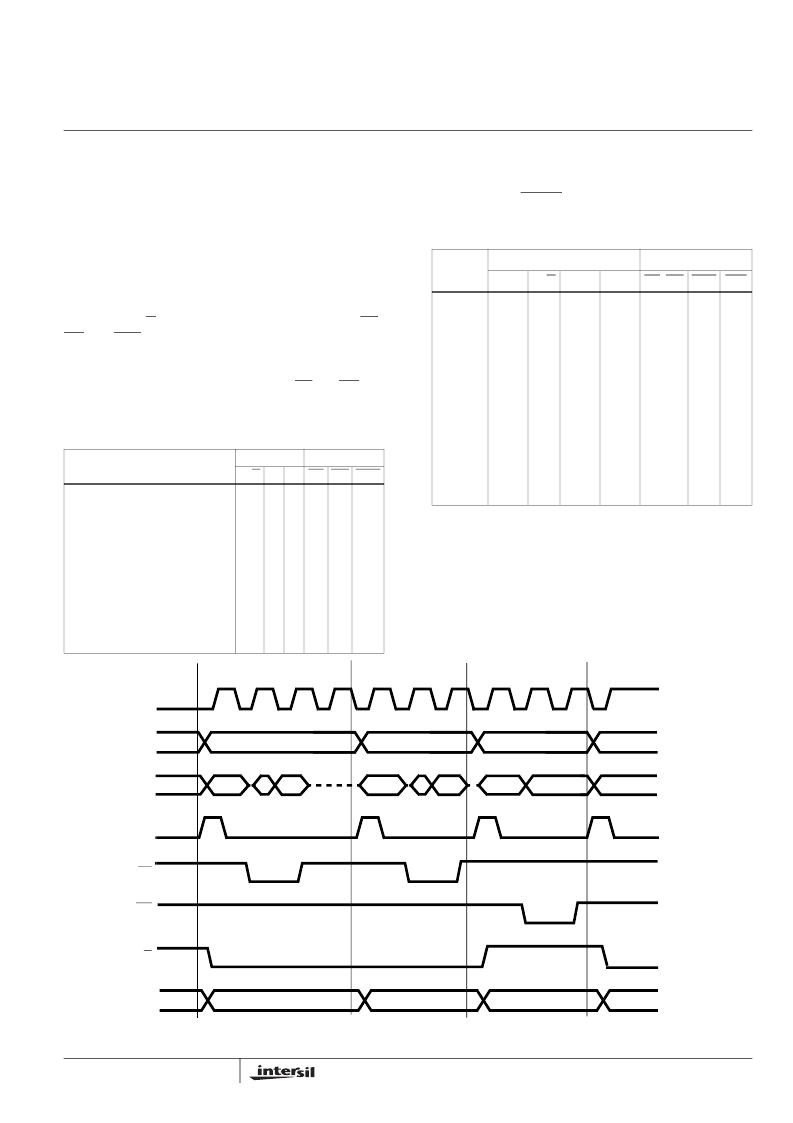

Basic System Timing

The HS-80C85RH has a multiplexed Data Bus. ALE is used

as a strobe to sample the lower 8-bits of address on the Data

Bus. Figure 15 shows an instruction fetch, memory read and

I/O write cycle (as would occur during processing of the OUT

instruction). Note that during the I/O write and read cycle that

the I/O port address is copied on both the upper and lower

half of the address.

There are seven possible types of machine cycles. Which of

these seven takes place is defined by the status of the three

status lines (lO/M, S1, S0) and the three control signals (RD,

WR, and INTA). (See Table 10.) The status lines can be

used as advanced controls (for device selection, for

example), since they become active at the T1 state, at the

outset of each machine cycle. Control lines RD and WR are

used as command lines since they become active when the

transfer of data is to take place.

A machine cycle normally consists of three T states, with the

exception of OPCODE FETCH, which normally has either

four or six T states (unless WAIT or HOLD states are forced

by the receipt of READY or HOLD inputs). Any T state must

be one of ten possible states, shown in Table 11.

TABLE 5. HS-80C85RH MACHINE CYCLE CHART

MACHINE CYCLE

Opcode Fetch (OF)

Memory Read (MR)

Memory Write (MW)

I/O Read

I/O Write

Acknowledge

of INTR

Bus Idle

STATUS

IO/M S1 S0 RD WR INTA

0

1

1

0

1

0

0

0

1

1

1

0

1

0

1

1

1

1

CONTROL

0

0

1

0

1

1

1

1

0

1

0

1

1

1

1

1

1

0

(IOR)

(IOW)

(INA)

(BI)

DAD Ack. of

RST, TRAP

HALT

0

1

1

1

0

0

1

0

1

1

1

1

1

1

1

TS

TS

TS

TABLE 6. HS-80C85RH MACHINE STATE CHART

MACHINE

STATE

STATUS AND BUSES

CONTROL

S1, S0 IO/M

A8-15

AD0-7 RD, WR INTA ALE

T1

X

X

X

X

1

1

1

T2

X

X

X

X

X

X

0

TWAIT

X

X

X

X

X

X

0

T3

X

X

X

X

X

X

0

T4

1

0

X

TS

1

1

0

T5

1

0

X

TS

1

1

0

T6

1

0

X

TS

1

1

0

TRESET

X

TS

TS

TS

TS

1

0

THALT

0

TS

TS

TS

TS

1

0

THOLD

X

TS

TS

TS

TS

1

0

0 = Logic “0”

1 = Logic “1”

TS = High Impedance

X = Unspecified

ALE not generated during 2nd and 3rd machine cycles of DAD

instruction.

IO/M = 1 during T4, T6 of INA machine cycle.

M1

M3

M2

T1

T2

T3

T4

T1

T2

T3

T1

T2

T3

T

CLK

A8-A15

AD0-7

ALE

RD

WR

IO/M

STATUS

PCH (HIGH ORDER ADDRESS)

(PC + 1)H

IO PORT

IO PORT

(PC+1)L

PCL

(LOW ORDER

ADDRESS)

DATA FROM

MEMORY

(INSTRUCTION)

DATA FROM

MEMORY (I/O

PORT ADDRESS)

DATA TO

MEMORY OR

PERIPHERAL

S1-S0 (FETCH)

10 (READ)

01 WRITE

11

FIGURE 15. 80C85RH BASIC SYSTEM TIMING

HS-80C85RH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HS1-80C85RH-Q | Radiation Hardened 8-Bit CMOS Microprocessor |

| HS1-81C55RH-8 | Radiation Hardened 256 x 8 CMOS RAM |

| HS1-81C55RH-Q | Radiation Hardened 256 x 8 CMOS RAM |

| HS1-81C56RH-8 | Radiation Hardened 256 x 8 CMOS RAM |

| HS1-81C56RH-Q | Radiation Hardened 256 x 8 CMOS RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HS1-80C85RH-Q | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened 8-Bit CMOS Microprocessor |

| HS1-80C86RH | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened 16-Bit CMOS Microprocessor |

| HS1-80C86RH/PROTO | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| HS1-80C86RH-8 | 制造商:Intersil Corporation 功能描述:MPU 16BIT CMOS 5MHZ 40PIN SBCDIP - Rail/Tube |

| HS1-80C86RH-Q | 制造商:Intersil Corporation 功能描述:MPU 16BIT CMOS 5MHZ 40PIN SBCDIP - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。