- 您現在的位置:買賣IC網 > PDF目錄385403 > HT82J97E-28SOP-A (Holtek Semiconductor Inc.) USB Joystick Encoder 8-Bit OTP MCU PDF資料下載

參數資料

| 型號: | HT82J97E-28SOP-A |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | USB Joystick Encoder 8-Bit OTP MCU |

| 中文描述: | USB搖桿編碼器8位微控制器檢察官辦公室 |

| 文件頁數: | 10/46頁 |

| 文件大小: | 314K |

| 代理商: | HT82J97E-28SOP-A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

HT82J97E

Rev. 1.30

10

May 10, 2004

abled, all the executions related to the WDT result in no

operation.

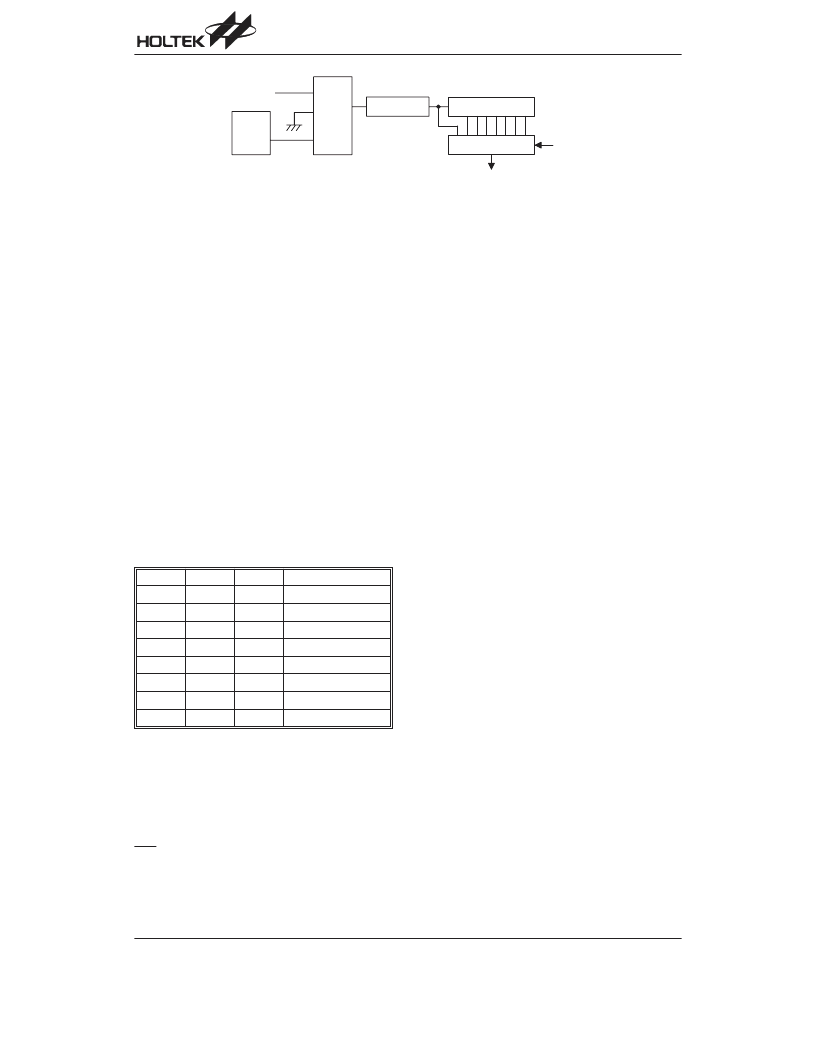

Once the internal WDT oscillator (RC oscillator with a

period of 31 s/5V normally) is selected, it is first divided

by 256 (8-stage) to get the nominal time-out period of

8ms/5V. This time-out period may vary with tempera-

tures, VDD and process variations. By invoking the

WDT prescaler, longer time-out periods can be realized.

Writing data to WS2, WS1, WS0 (bits 2, 1, 0 of the

WDTS) can give different time-out periods. If WS2,

WS1, and WS0 are all equal to 1, the division ratio is up

to 1:128, and the maximum time-out period is 1s/5V. If

the WDT oscillator is disabled, the WDT clock may still

come from the instruction clock and operates in the

same manner except that in the HALT state the WDT

may stop counting and lose its protecting purpose. In

this situation the logic can only be restarted by external

logic. The high nibble and bit 3 of the WDTS are re-

served for user defined flags, which can only be set to

10000 (WDTS.7~WDTS.3).

If the device operates in a noisy environment, using the

on-chip 32kHz RC oscillator (WDT OSC) is strongly rec-

ommended, since the HALT will stop the system clock.

WS2

WS1

WS0

Division Ratio

0

0

0

1:1

0

0

1

1:2

0

1

0

1:4

0

1

1

1:8

1

0

0

1:16

1

0

1

1:32

1

1

0

1:64

1

1

1

1:128

WDTS Register

The WDT overflow under normal operation will initialize

a chip reset and set the status bit TO . But in the

HALT mode, the overflow will initialize a warm reset

and only the PC and SP are reset to zero. To clear the

contents of the WDT (including the WDT prescaler),

threemethodsareadopted;externalreset(alowlevelto

RES), software instruction and a

HALT

instruction.

The software instruction include CLR WDT and the

other set

two types of instruction, only one can be active depend-

CLR WDT1 and CLR WDT2 . Of these

ing on the ROM code option

CLR WDT times selec-

tion option . If the CLR WDT is selected (i.e. CLRWDT

times is equal to one), any execution of the CLR WDT

instruction will clear the WDT. In the case that CLR

WDT and CLR WDT are chosen (i.e. CLRWDT times

is equal to two), these two instructions must be exe-

cuted to clear the WDT; otherwise, the WDT may reset

the chip as a result of time-out.

Power Down Operation

HALT

The HALT mode is initialized by the HALT instruction

and results in the following:

The system oscillator will be turned off but the WDT

oscillator remains running (if the WDT oscillator is se-

lected).

The contents of the on-chip RAM and registers remain

unchanged.

The WDT and WDT prescaler will be cleared and re-

counted again (if the WDT clock is from the WDT os-

cillator).

All of the I/O ports remain in their original status.

The PDF flag is set and the TO flag is cleared.

The system can leave the HALT mode by means of an

external reset, an interrupt, an external falling edge sig-

nal on port A or a WDT overflow. An external reset

causes a device initialization and the WDToverflow per-

forms a warm reset . After the TO and PDF flags are

examined, the cause for chip reset can be determined.

The PDF flag is cleared by a system power-up or exe-

cuting the CLR WDT instruction and is set when exe-

cuting the HALT instruction. The TO flag is set if the

WDT time-out occurs, and causes a wake-up that only

resets the PC and SP; the others remain in their original

status.

The port A wake-up and interrupt methods can be con-

sidered as a continuation of normal execution. Each bit

in port A can be independently selected to wake-up the

devicebymaskoption.AwakeningfromanI/Oportstim-

ulus, the program will resume execution of the next in-

struction. If it awakens from an interrupt, two sequence

may occur. If the related interrupt is disabled or the inter-

rupt is enabled but the stack is full, the program will re-

sume execution at the next instruction. If the interrupt is

enabled and the stack is not full, the regular interrupt re-

sponse takes place. If an interrupt request flag is set to

1 before entering the HALT mode, the wake-up func-

tion of the related interrupt will be disabled. Once a

!

(

,

> ) *

9 6

(

+

(

!

,

1 6

(

9 6

6 (

+

(

6

+

. +

"

,

+

Watchdog Timer

相關PDF資料 |

PDF描述 |

|---|---|

| HT82K28 | Win98 Keyboard Encoder |

| HT82K28A | Win98 Keyboard Encoder |

| HT82K628A | Windows 2000 Keyboard Encoder(Windows 2000操作系統鍵盤編碼器) |

| HT82K628 | Windows 2000 Keyboard Encoder |

| HT82K629A | Windows 2000 USB+PS/2 Keyboard Encoder |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HT82K19 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| HT82K28 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Win98 Keyboard Encoder |

| HT82K28A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Win98 Keyboard Encoder |

| HT82K28A_02 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Win98 Keyboard Encoder |

| HT82K628 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Windows 2000 Keyboard Encoder |

發布緊急采購,3分鐘左右您將得到回復。