- 您現在的位置:買賣IC網 > PDF目錄385404 > HT82V26A (Holtek Semiconductor Inc.) 16-Bit CCD/CIS Analog Signal Processor PDF資料下載

參數資料

| 型號: | HT82V26A |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 16-Bit CCD/CIS Analog Signal Processor |

| 中文描述: | 16位防治荒漠化公約/獨聯體模擬信號處理器 |

| 文件頁數: | 7/17頁 |

| 文件大小: | 170K |

| 代理商: | HT82V26A |

HT82V26A

Rev. 1.00

7

August 16, 2005

D8

D7

D6

D5

D4

D3

D2

D1

D0

Set to 0 Set to 0 Set to 1

3 channels CDS operation Clamp bias Power-down

Output delay

1 byte out

(High-byte

only)

1=On*

1=CDS mode* 1=4V*

1=On

1=On

1=On

0=Off

0=SHA mode

0=3V

0=Off (Normal)* 0=Off*

0=Off*

Configuration Register Settings

Note: * Power-on default value

MUX Register

The MUX register controls the sampling channel order and the 2-channel mode configuration in the HT82V26A. Bits

D8 should always be set low. Bit D7 is used when operating in the 3-channel mode or the 2-channel mode. Setting bit

D7 high will sequence the MUX to sample the red channel first, then the green channel, and then the blue channel.

When in the 3-channel mode, the CDSCLK2 rising edge always resets the MUX to sample the red channel first (see

timing diagrams). When bit D7 is set low, the channel order is reversed to blue first, green second, and red third. The

CDSCLK2 rising edge will always reset the MUX to sample the blue channel first. Bits D6, D5 and D4 are used when

operating in 1 or 2-channel mode. Bit D6 is set high to sample the red channel. Bit D5 is set high to sample the green

channel. Bit D4 is set high to sample the blue channel. The MUX will remain stationary during 1-channel mode. The two

channel mode is selected by setting two of the channel select bits (D4~D6) high. The MUX samples the channels in the

order selected by bit D7. Bits D0~D3 are used for controlling CDSCLK1, CDSCLK2 and ADCCLK internal delay.

D8

D7

D6

D5

D4

D3

D2

D1

D0

Set to 0

MUX Order

Channel Select

Enable Delay CDS1 Delay

CDS2 Delay

ADCK Delay

1=R-G-B*

0=B-G-R

1=RED*

0=Off

1=GREEN

0=Off*

1=BLUE

0=Off*

0=Off

0=2ns*

0=2ns*

0=0ns*

1=On*

1=4ns

1=4ns

1=2ns

MUX Register Settings

Note: * Power-on default value

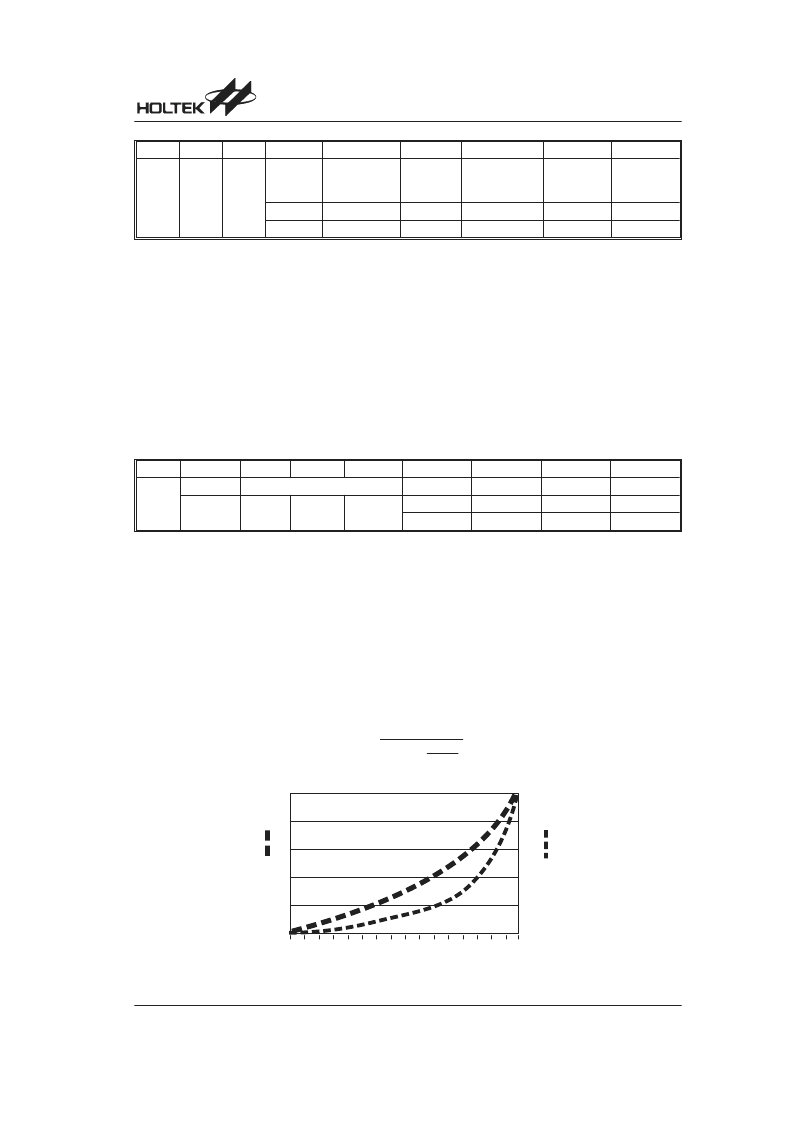

PGA Gain Registers

TherearethreePGAregistersforuseinindividuallyprogrammingthegaininthered,greenandbluechannels.BitsD8,

D7 and D6 in each register must be set low, and bits D5 through D0 control the gain range in 64 increments. See figure

for a graph of the PGAgain versus PGAregister code. The coding for the PGAregisters is a straight binary, with an all

zero words corresponding to the minimum gain setting (1x) and an all one word corresponding to the maximum gain

setting (5.85x).

The HT82V26Auses one Programmable Gain Amplifier (PGA) for each channel. Each PGAhas a gain range from 1x

(0dB) to 5.85x (15.3dB), adjustable in 64 steps. The Figure shows the PGAgain as a function of the PGAregister code.

Although the gain curve is approximately linear in dB, the gain in V/V varies in nonlinear proportion with the register

code, according to the following the equation: Gain=

5.85

1

4.85x(63

G

63

)

+

-

Where G is the decimal value of the gain register contents, and varies from 0 to 63.

- 2 2

2 2 - 1 2 2 - 0 2 2 - % 2 2 - 2 2

2 2 0 1 2 2 0 0 2 2 0 % 2 2 / - 2 2 /

2 2 1

1

0

%

/

-

1

/ % /

/ 1

0 1

1

- 1

1

"

5

2

"

)

2

2 7

!

2

2

# '

!

PGA Gain Transfer Function

相關PDF資料 |

PDF描述 |

|---|---|

| HT82V26 | 16-Bit CCD/CIS Analog Signal Processor |

| HT82V36 | 16-Bit CCD/CIS Analog Signal Processor |

| HT82V731 | Audio D/A Converter |

| HT82V732 | Protective Eyeglasses |

| HT82V733 | 240mA Audio Power Amp |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HT82V36 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:16-Bit CCD/CIS Analog Signal Processor |

| HT82V38 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:16-Bit CCD/CIS Analog Signal Processor |

| HT82V42 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Single-channel 16-Bit CCD/CIS Analog Signal Processor |

| HT82V42_10 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:Single-channel 16-Bit CCD/CIS Analog Signal Processor |

| HT82V46 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:16-Bit, 45MSPS, 3-Channel CCD/CIS Analog Signal Processor |

發布緊急采購,3分鐘左右您將得到回復。