- 您現在的位置:買賣IC網 > PDF目錄385405 > HT86384 (Holtek Semiconductor Inc.) Voice Synthesizer 8-Bit MCU PDF資料下載

參數資料

| 型號: | HT86384 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | Voice Synthesizer 8-Bit MCU |

| 中文描述: | 語音合成器8位微控制器 |

| 文件頁數: | 22/39頁 |

| 文件大小: | 368K |

| 代理商: | HT86384 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

HT86XXX

Rev. 1.70

22

May 6, 2004

As an interrupt is serviced, a control transfer occurs by

pushing the program counter onto the stack and then

branching to subroutines at the specified location(s) in

the program memory. Only the program counter is

pushed onto the stack. The programmer must save the

contents of the register or status register (STATUS) in

advance if they are altered by an interrupt service pro-

gram which corrupts the desired control sequence.

External interrupt is triggered by a high-to-low/

low-to-high transition of INT pin which sets the related

interrupt request flag (EIF:bit 4 of INTC). When the inter-

rupt is enabled, and the stack is not full and the external

interrupt is active, a subroutine call to location 04H will

occur. The interrupt request flag (EIF) and EMI bits will

be cleared to disable other interrupts.

The internal Timer/Event Counter 0 interrupt is initial-

ized by setting the Timer/Event counter 0 interrupt re-

quest flag (T0F:bit 5 of INTC), caused by a Timer/Event

Counter 0 overflow. When the interrupt is enabled, and

the stack is not full and the T0F bit is set, a subroutine

call to location 08H will occur. The related interrupt re-

quest flag (T0F) will be reset and the EMI bit cleared to

disable further interrupts.

The internal Timer/Event Counter 1 interrupt is initial-

ized by setting the Timer/Event Counter 1 interrupt re-

quest flag (T1F:bit 6 of INTC), caused by a Timer/Event

Counter 1 overflow. When the interrupt is enabled, and

the stack is not full and the T1F bit is set, a subroutine

call to location 0CH will occur. The related interrupt re-

quest flag (T1F) will be reset and the EMI bit cleared to

disable further interrupts.

The internal Timer Counter 2 interrupt is initialized by

setting the Timer Counter 2 interrupt request flag

(T2F:bit 0 of INTCH), caused by a Timer Counter 2 over-

flow. When the interrupt is enabled, and the stack is not

full and the T2F bit is set, a subroutine call to location

10H will occur. The related interrupt request flag (T2F)

will be reset and the EMI bit cleared to disable further in-

terrupts.

The internal Timer Counter 3 interrupt is initialized by

setting the Timer Counter 3 interrupt request flag

(T3F:bit 1 of INTCH), caused by a Timer Counter 3 over-

flow. When the interrupt is enabled, and the stack is not

full and the T3F bit is set, a subroutine call to location

14H will occur. The related interrupt request flag (T3F)

will be reset and the EMI bit cleared to disable further in-

terrupts.

During the execution of an interrupt subroutine, other in-

terrupt acknowledges are held until the RETI instruction

is executed or the EMI bit and the related interrupt con-

trol bit are set to 1 (of course, if the stack is not full). To

return from the interrupt subroutine, the RET or RETI in-

struction may be invoked. RETI will set the EMI bit to en-

able an interrupt service, but RET will not.

Interrupts occurring in the interval between the rising

edges of two consecutive T2 pulses, will be serviced on

the latter of the two T2 pulses, if the corresponding inter-

rupts are enabled. In the case of simultaneous requests,

the following table shows the priority that is applied.

These can be masked by resetting the EMI bit.

The Timer/Event Counter 0/1 interrupt request flag

(T0F/T1F) which enables Timer/Event Counter 0/1 con-

trol bit (ET0I/ET1I), the Timer Counter 2/3 interrupt re-

quest flag (T2F/T3F) which enables Timer Counter 2/3

control bit (ET2I/ET3I), and external interrupt request

flag (EIF) which enables external interrupt control bit

(EEI) form the interrupt control register (INTC:0BH and

INTCH:1EH). EMI, EEI, ET0I, ET1I, ET2I, and ET3I are

used to control the enabling/disabling of interrupts.

These bits prevent the requested interrupt begin ser-

viced. Once the interrupt request flags (T0F, T1F, T2F,

T3F, EIF) are set, they will remain in the INTC/INTCH

register until the interrupts are serviced or cleared by a

software instruction.

It is recommended that application programs do not use

CALL subroutines within an interrupt subroutine. Inter-

rupts often occur in an unpredictable manner or need to

be serviced immediately in some applications. If only

one stack is left and the interrupt enable is not well con-

trolled, once a CALL subroutine if used in the interrupt

subroutine will corrupt the original control sequence.

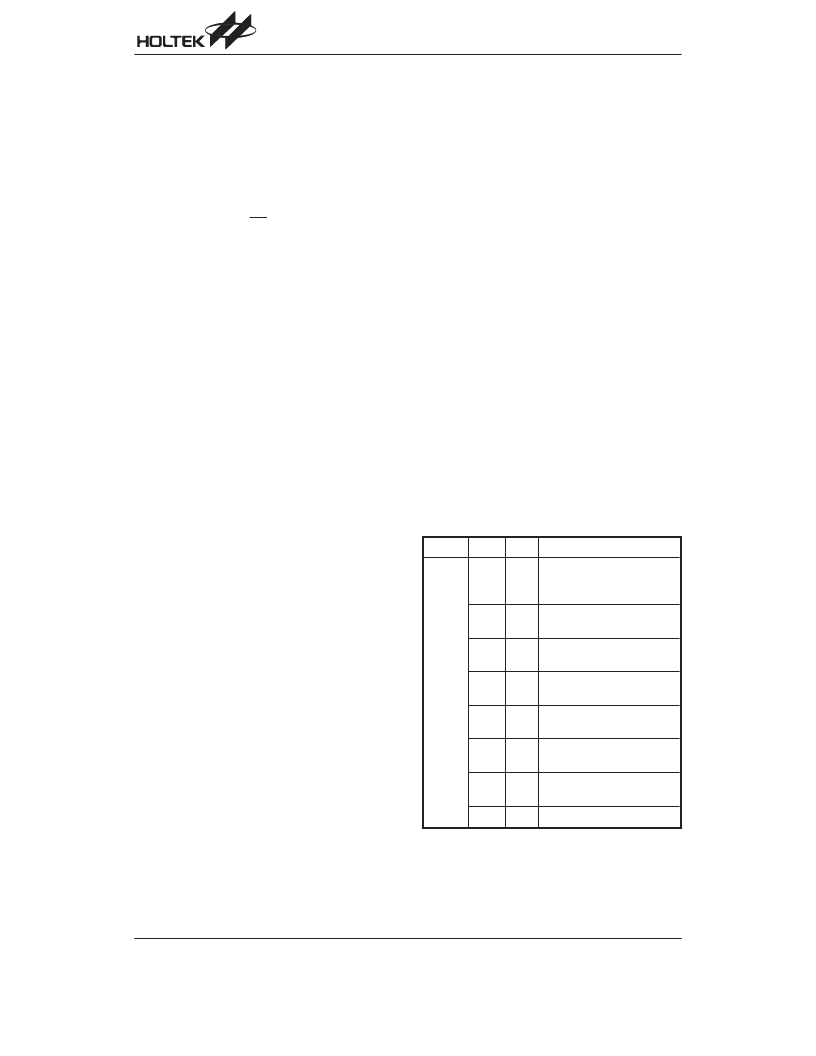

Register Bit No. Label

Function

INTC

(0BH)

0

EMI

Controls the master (global)

interrupt

(1= enabled; 0= disabled)

1

EEI

Controlstheexternalinterrupt

(1= enabled; 0= disabled)

2

ET0I

Controls the timer 0 interrupt

(1= enabled; 0= disabled)

3

ET1I

Controls the timer 1 interrupt

(1= enabled; 0= disabled)

4

EIF

Externalinterruptrequestflag

(1= active; 0= inactive)

5

T0F

Timer 0 request flag

(1= active; 0= inactive)

6

T1F

Timer 1 request flag

(1= active; 0= inactive)

7

Unused bit, read as 0

INTC0 Register

相關PDF資料 |

PDF描述 |

|---|---|

| HT86576 | Voice Synthesizer 8-Bit MCU |

| HT86R192 | Voice Synthesizer 8-Bit OTP MCU |

| HT86R384 | Voice Synthesizer 8-Bit OTP MCU |

| HT86XXX | 8-Bit Voice Synthesizer MCU |

| HT8950 | Voice Modulator |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HT86384(68PLCC) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| HT8650 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:IC-MESSAGE REMINDER IC |

| HT8650(28DIP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Speech Synthesizer |

| HT8650(28SDIP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Speech Synthesizer |

| HT8650(28SOIC) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Speech Synthesizer |

發(fā)布緊急采購,3分鐘左右您將得到回復。